# DATA HANDB()() () ()

ICs for Telecom

Subscriber Sets

Cordless Telephones

Mobile/cellular

Radio Pagers

CA3089 to PCD4413

Philips Semiconductors

PHILIPS

| , |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

#### ICs for Telecom Subscriber sets Cordless Telephones Mobile/Cellular Radio Pagers

| Part a<br>Selection Guide                                                                                    | page |

|--------------------------------------------------------------------------------------------------------------|------|

| Functional index                                                                                             | 5    |

| Numerical index                                                                                              | 13   |

| Comparison of the TEA1060 family                                                                             | 25   |

| Comparison of microcontrollers for telephone sets                                                            | 26   |

| General                                                                                                      |      |

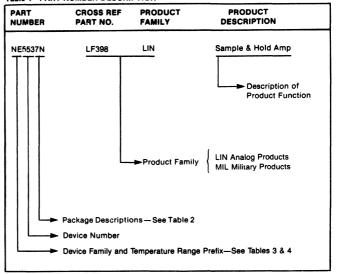

| Product status definitions for type numbers with prefixes CA, MC, NE, SA and SE                              | 29   |

| Ordering information for type numbers with prefixes CA, MC, NE, SA and SE                                    | 30   |

| Type designation for type numbers with prefixes FCB, FCF, OM, PCA, PCB, PCD, PCF, TDA, TDD, TEA, UAA and UMA | 31   |

| Rating systems for type numbers with prefixes FCB, FCF, OM, PCA, PCB, PCD, PCF, TDA, TDD, TEA, UAA and UMA   | 33   |

| Handling MOS devices                                                                                         | 35   |

| Device data CA3089 to PCD4413                                                                                |      |

| Part b                                                                                                       |      |

| Selection Guide                                                                                              |      |

| Functional index                                                                                             | 901  |

| Numerical index                                                                                              | 909  |

| Device data                                                                                                  |      |

| PCD4413A to 74HC/HCT7046A                                                                                    |      |

| Package information                                                                                          |      |

| Package outlines                                                                                             | 1687 |

| Soldering                                                                                                    | 1727 |

#### **SELECTION GUIDE**

Functional index Numerical index Comparison of the TEA1060 family Comparison of microcontrollers for telephone sets •

## Functional index

#### **FUNCTIONAL INDEX**

| type number         | description                                                               | page  |

|---------------------|---------------------------------------------------------------------------|-------|

| AMPLIFIERS          |                                                                           |       |

| NE542               | dual low-noise preamplifier                                               | 69    |

| NE/SA5204           | wideband high-frequency amplifier                                         | 231   |

| NE/SA/SE5205        | wideband high-frequency amplifier                                         | 241   |

| NE/SA5209           | wideband variable gain amplifier                                          | 253   |

| NE/SA5230           | low-voltage operational amplifier                                         | 267   |

| NE/SA5234           | matched quad high-performance low-voltage operational amplifier           | 279   |

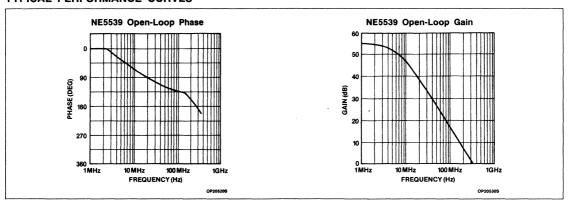

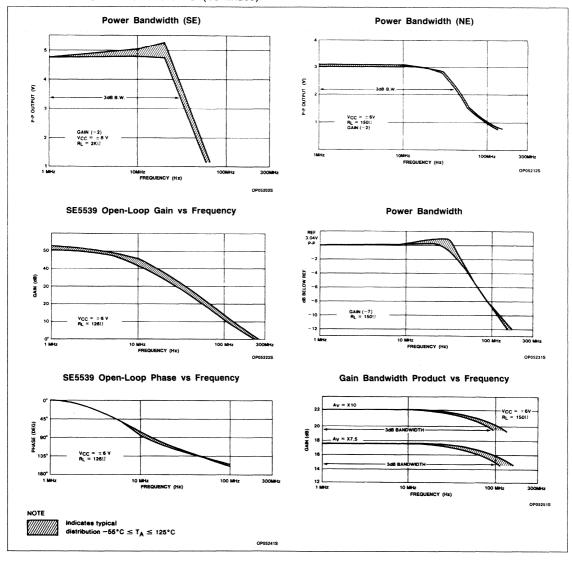

| NE/SE5539           | high-frequency operational amplifier                                      | 285   |

| TDA1011             | 2 to 6 W audio power amplifier                                            | 1267  |

| TDA1011A            | 2 to 6 W audio power amplifier                                            | 1279  |

| TDA1015T            | 0.5 W audio power amplifier                                               | 1279  |

| TDA7050             | 140 mW BTL or 2 x 75 mW mono/stereo audio power amplifier; low-voltage    | 1305  |

| 1DA1030             | (in plastic DIL8)                                                         | 1305  |

| TDA7050T            | 140 mW BTL or 2 x 75 mW mono/stereo audio power amplifier; low-voltage    | 1309  |

| 12/1/0001           | (in SO8 plastic mini-pack)                                                | 1309  |

| TDA7052             | 1 W BTL mono audio amplifier                                              | 1313  |

| TDA7053             | 2 x 1 W BTL portable/mains-fed stereo power amplifier                     | 1319  |

| 1DA1000             | 2 X T W BTE portable/mains-red stereo power ampliner                      | 1319  |

| AUDIO AND DATA PRO  | CESSORS                                                                   |       |

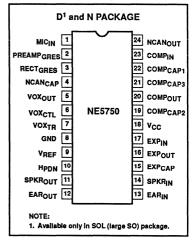

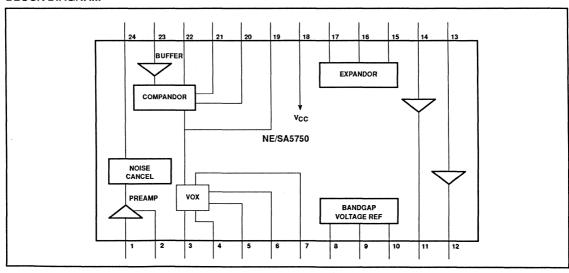

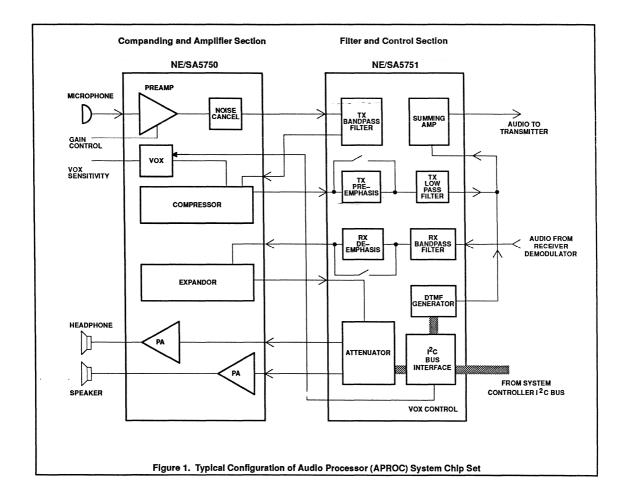

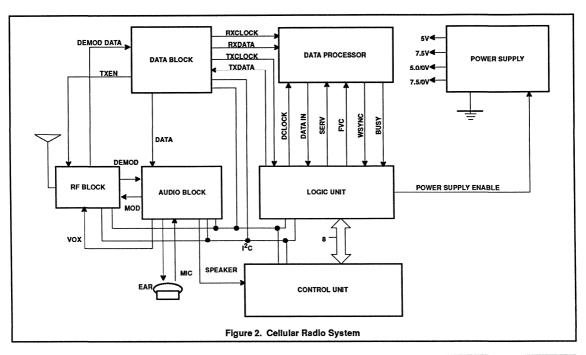

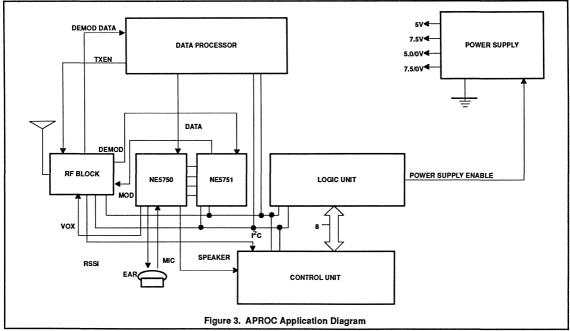

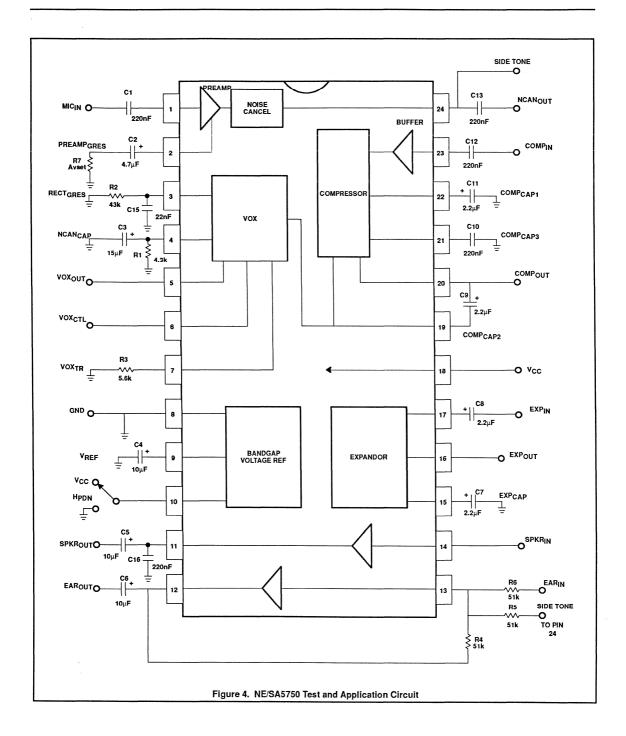

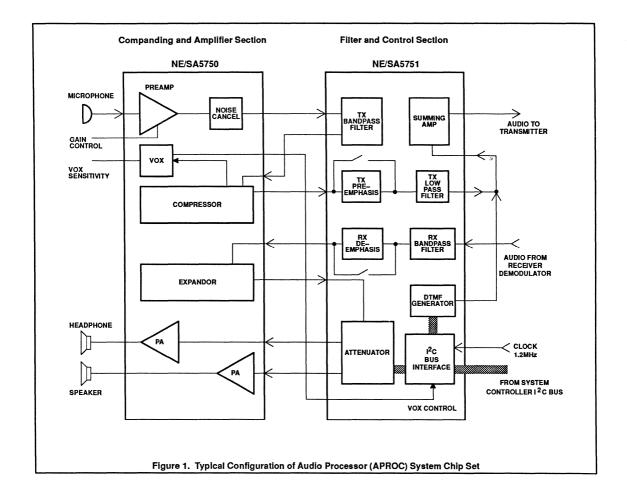

| NE/SA5750           | audio processor - companding and amplifier section                        | 293   |

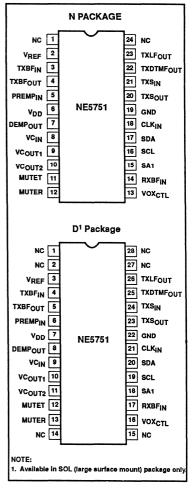

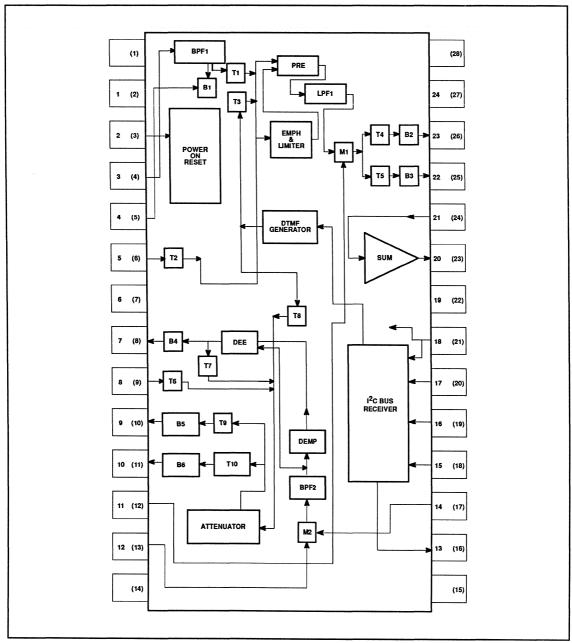

| NE/SA5751           | audio processor - filter and control section                              | 301   |

| UMA1000T            | data processor for AMPS/TACS cellular radio (DPROC); I <sup>2</sup> C-bus | 1561  |

| CALL PROGRESS DECO  | ONER                                                                      |       |

|                     |                                                                           | 0.1.1 |

| NE5900              | call progress decoder                                                     | 311   |

| CLOCK/CALENDAR      | •                                                                         |       |

| PCF8573             | clock/calendar with serial I/O; I <sup>2</sup> C-bus                      | 1163  |

| PCF8583             | clock/calendar with 256 x 8-bit static RAM; I <sup>2</sup> C-bus          | 1233  |

| 1 01 0000           | Clock calculat with 250 x 0-bit static (1714), 1-0-bus                    | 1200  |

| COMPANDORS          |                                                                           |       |

| NE570/571/SA571     | compandor                                                                 | 113   |

| NE/SA572            | programmable analog compandor                                             | 123   |

| NE/SA575            | low-voltage compandor                                                     | 131   |

| NE/SA575            | low-voltage compandor in very small outline package (VSOP)                | 143   |

| NE/SA577            | unity gain level programmable low-power compandor                         | 153   |

| NE/SA578            | unity gain level programmable low-power compandor                         | 157   |

| DATA CONVEDEION     |                                                                           |       |

| DATA CONVERSION     |                                                                           |       |

| PCF8591             | 8-bit ADC/DAC; I <sup>2</sup> C-bus                                       | 1239  |

| DIGITAL SIGNAL PROC | ESSORS                                                                    |       |

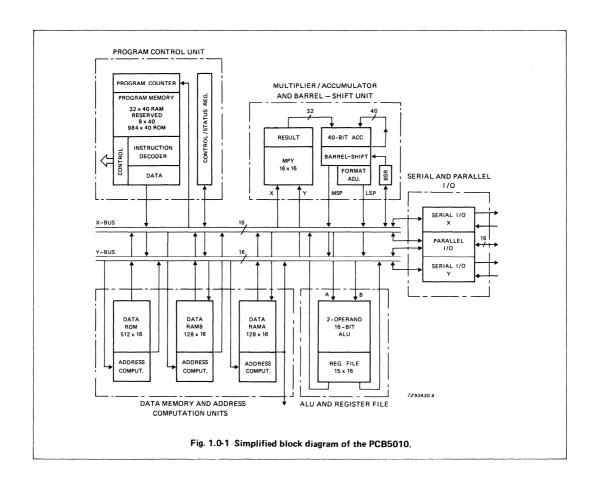

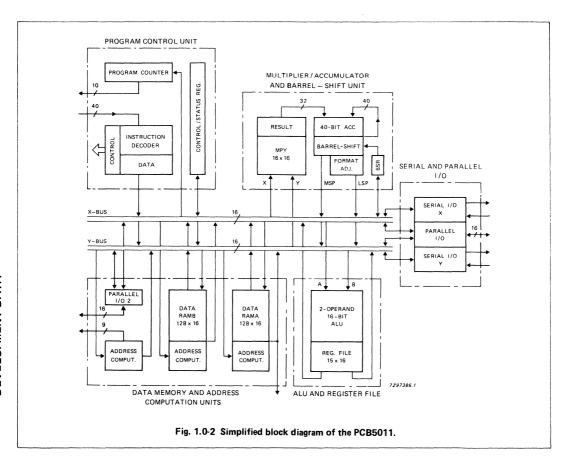

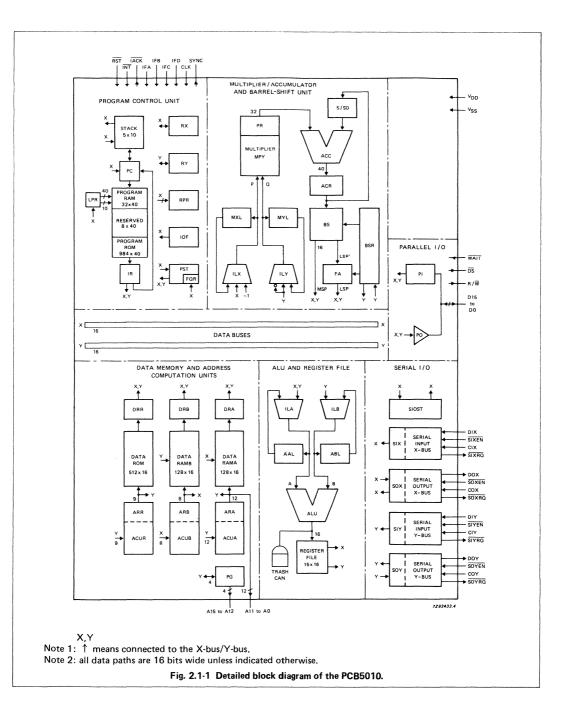

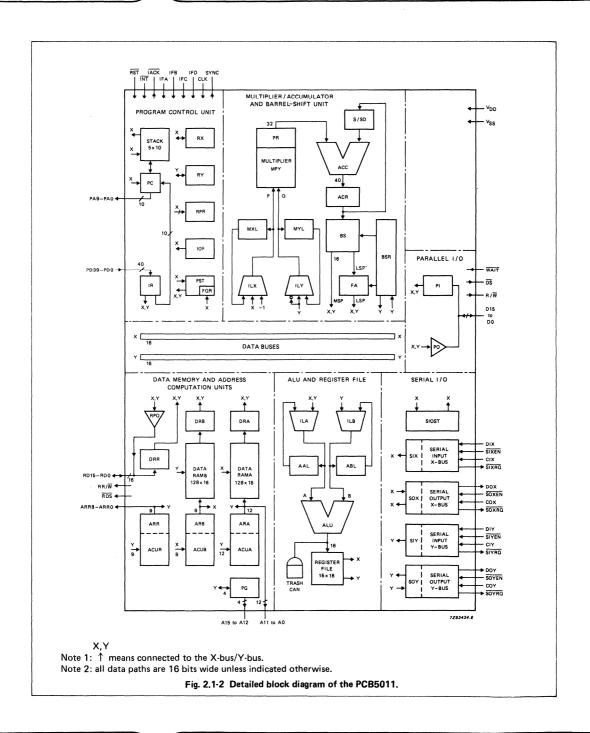

| PCB5010             |                                                                           |       |

| PCB5010<br>PCB5011  | single-chip digital signal processor                                      | 379   |

| I ODSUTT            | ROM-less version of PCB5010                                               | 379   |

# Functional index

| type number               | description                                                                                                                                                    | page         |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| DISPLAY DRIVERS           |                                                                                                                                                                |              |

| PCF21XX Family            | LCD duplex drivers                                                                                                                                             | 1025         |

| PCF2201<br>PCF8566        | LCD flat-panel row/column driver universal LCD driver for low multiplex rates (1:1 to 1:4) max. 96 segments;                                                   | 1041<br>1145 |

| FOI 0300                  | 12C-bus                                                                                                                                                        | 1143         |

| PCF8569                   | LCD column driver for dot matrix graphic displays at multiplex rates of 1:8 or 1:16: 40 outputs: I <sup>2</sup> C-bus                                          | 1151         |

| PCF8576                   | universal LCD driver for low multiplex rates (1:1 to 1:4) max, 160 segments;                                                                                   | 1191         |

| D050555111010101          | I <sup>2</sup> C-bus                                                                                                                                           | 4004         |

| PCF8577/A/C/CA<br>PCF8578 | LCD direct driver (32 segments) or duplex driver (64 segments); I <sup>2</sup> C-bus LCD row/column driver for dot matrix graphic displays; 40 outputs (24 are | 1201<br>1209 |

| FOI 0376                  | programmable); I <sup>2</sup> C-bus                                                                                                                            | 1203         |

| PCF8579                   | LCD column driver for dot matrix graphic displays; 40 column outputs;                                                                                          | 1219         |

|                           | I <sup>2</sup> C-bus                                                                                                                                           |              |

| DTMF GENERATORS/D         | IALLERS                                                                                                                                                        |              |

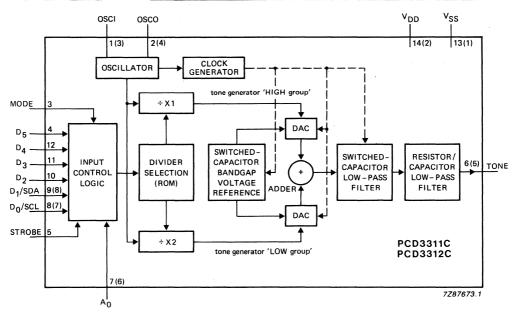

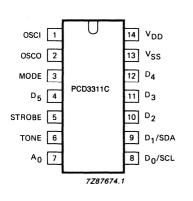

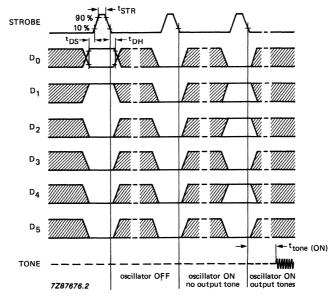

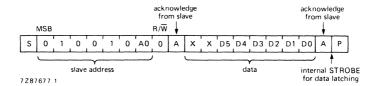

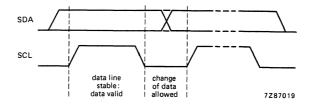

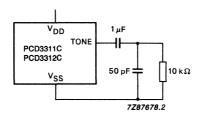

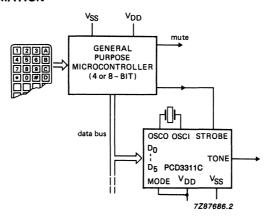

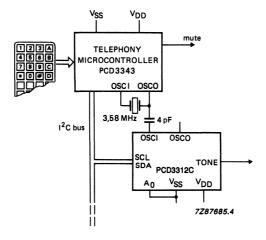

| PCD3311C/12C              | DTMF/modem/music tone generators with binary-coded parallel input or                                                                                           | 509          |

| 1 0000110/120             | serial data input; I <sup>2</sup> C-bus                                                                                                                        |              |

| PCD4420                   | pulse and DTMF dialler with redial for 4 x 4 keypad                                                                                                            | 977<br>987   |

| PCD4421                   | pulse and DTMF dialler with redial for 4 x 5 keypad                                                                                                            | 967          |

| DIALLER ICs               |                                                                                                                                                                |              |

| Pulse                     |                                                                                                                                                                |              |

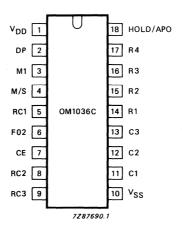

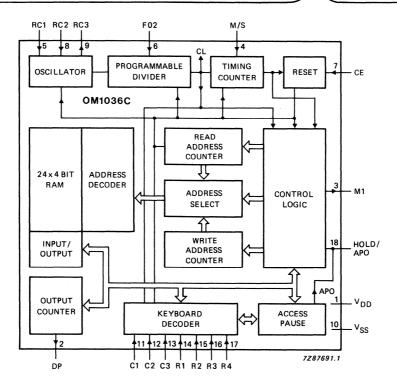

| OM1036C                   | dialler circuit with redial                                                                                                                                    | 319          |

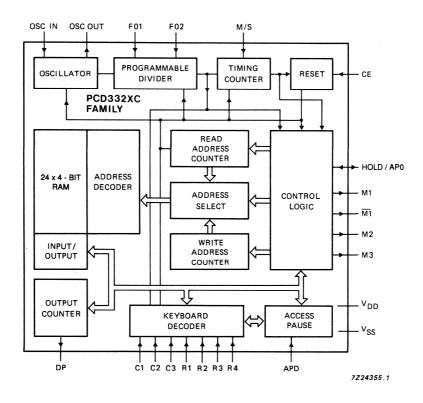

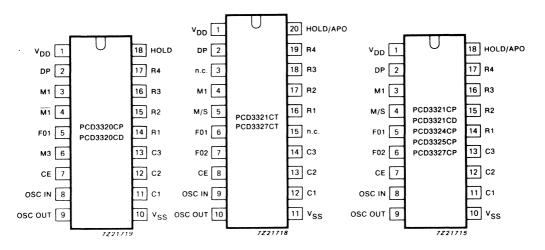

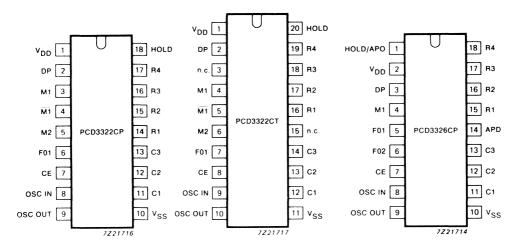

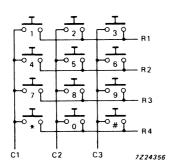

| PCD332XC Family           | pulse dialler circuits with redial                                                                                                                             | 531          |

|                           |                                                                                                                                                                |              |

| Pulse/DTMF                |                                                                                                                                                                |              |

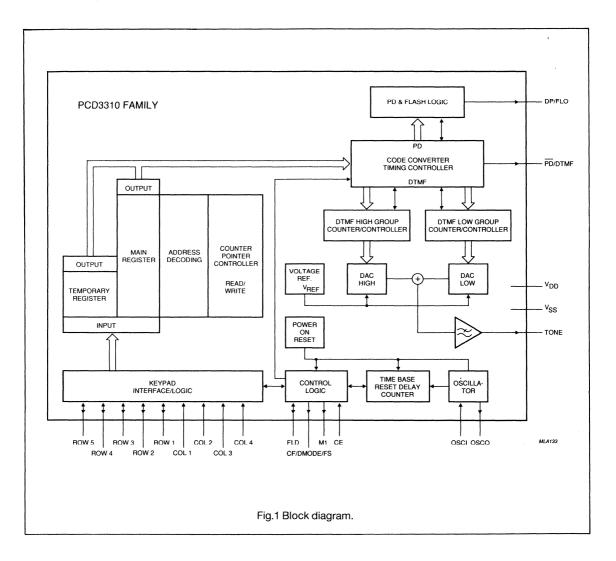

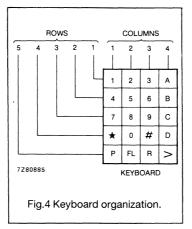

| PCD3310 Family            | pulse and DTMF dialler with redial                                                                                                                             | 485          |

| PCD3347                   | pulse/DTMF dialler with redial                                                                                                                                 | 741<br>867   |

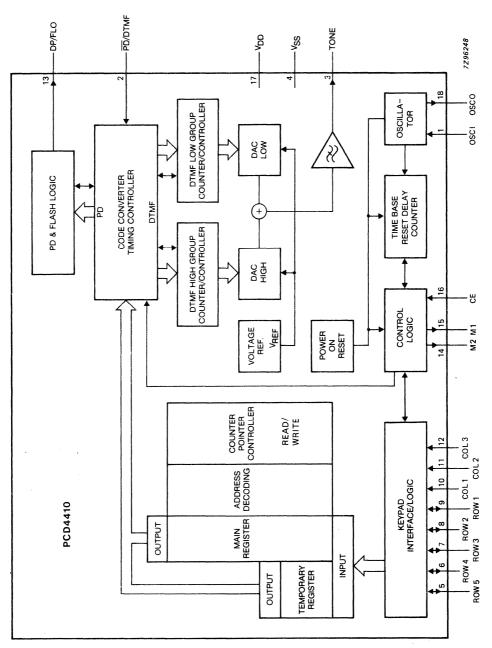

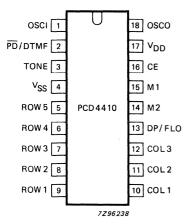

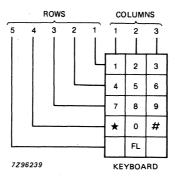

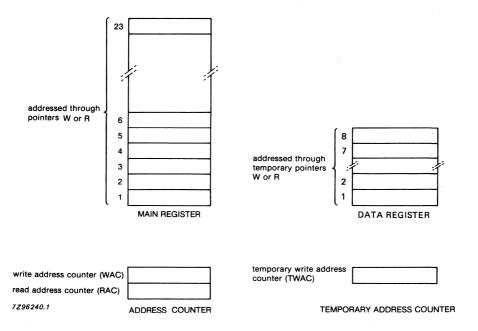

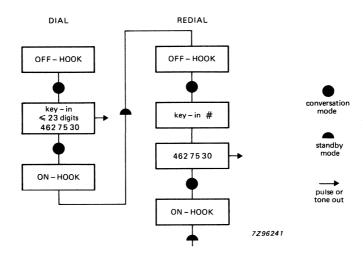

| PCD4410                   | pulse and DTMF dialler with redial; manual access pause; 3 x 4 keypad plus flash; mark/space ratio 2:1; tone burst 70/140 ms; data memory                      | 007          |

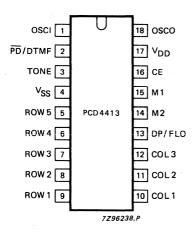

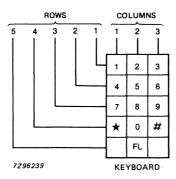

| PCD4413                   | variant of PCD4410 without redial; mark/space ratio 3:2; tone burst 70/70 ms                                                                                   | 883          |

| PCD4413A                  | PCD4413 with flash time of 255 ms                                                                                                                              | 923<br>937   |

| PCD4415<br>PCD4415A       | PCD4410 with 3 x 4 or 3 x 5 keypad; tone burst 70/70 ms<br>PCD4415 with mark/space ratio of 3:2                                                                | 957<br>957   |

|                           |                                                                                                                                                                |              |

| Repertory                 |                                                                                                                                                                |              |

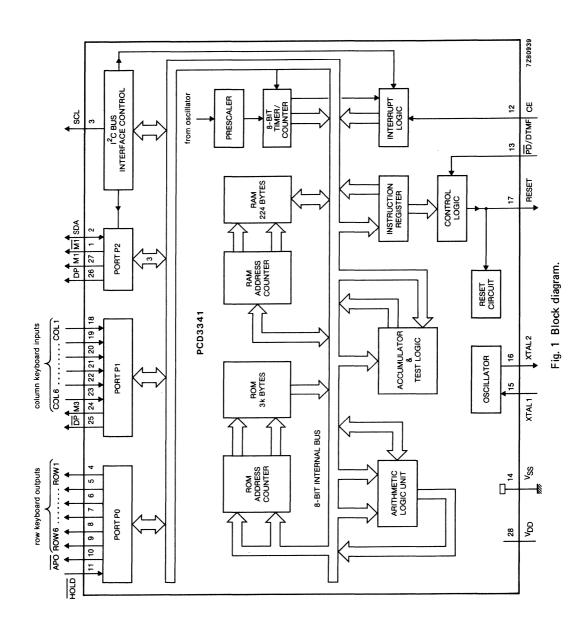

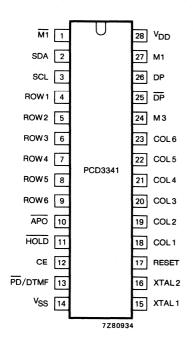

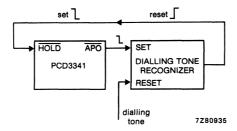

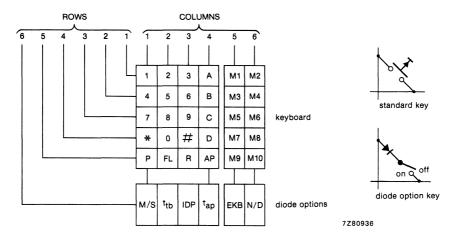

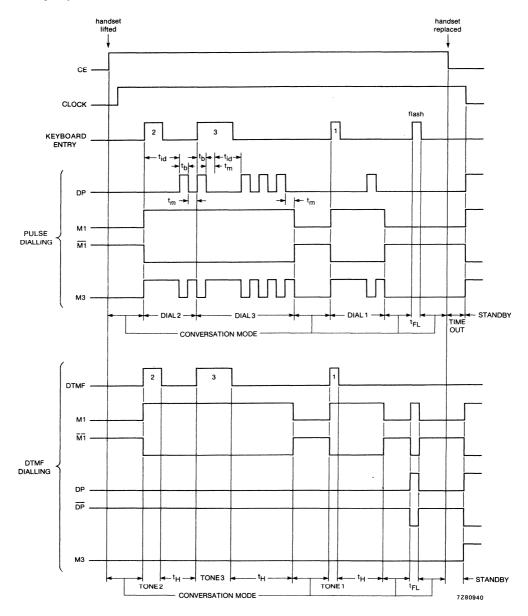

| PCD3341                   | advanced 10-100-number repertory pulse/DTMF dialler; LCD control;                                                                                              | 561          |

|                           | l <sup>2</sup> C-bus                                                                                                                                           | 551          |

|                           |                                                                                                                                                                |              |

| EXPANDERS                 |                                                                                                                                                                |              |

| PCF8574                   | remote 8-bit I/O expander; I <sup>2</sup> C-bus                                                                                                                | 1179         |

| PCF8574A                  | remote 8-bit I/O expander; I <sup>2</sup> C-bus; different slave address                                                                                       | 1179         |

#### Functional index

| type number          | description                                                                                                                                   | page         |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| FREQUENCY SYNTHES    | TITEDS                                                                                                                                        |              |

|                      |                                                                                                                                               |              |

| TDD1742T<br>UMA1010T | low-power frequency synthesizer (LOPSY) low-power universal frequency synthesizer for radio communications; 400                               | 1327<br>1591 |

| UMA1012T             | MHz to 1150 MHz; I <sup>2</sup> C-bus low-power universal frequency synthesizer for radio communications; 20 to 600 MHz; I <sup>2</sup> C-bus | 1605         |

|                      |                                                                                                                                               |              |

|                      | ICs (excluding microcontrollers)                                                                                                              |              |

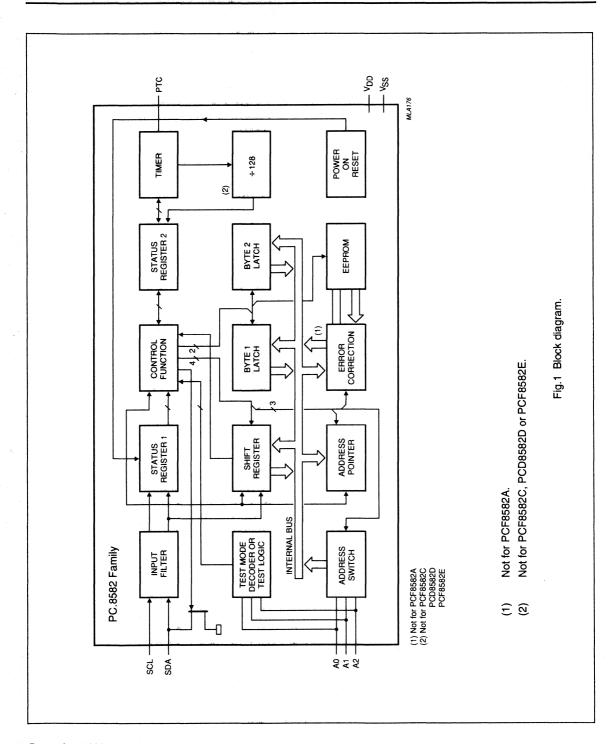

| PC.8582 Family       | 256 x 8-bit static EEPROMS; CMOS; for automotive applications                                                                                 | 345          |

| PCD3311C/12C         | DTMF/modem/music tone generators with binary-coded parallel input or<br>serial data input                                                     | 509          |

| PCD3341              | advanced 10-100-number repertory pulse/DTMF dialler; LCD control                                                                              | 561          |

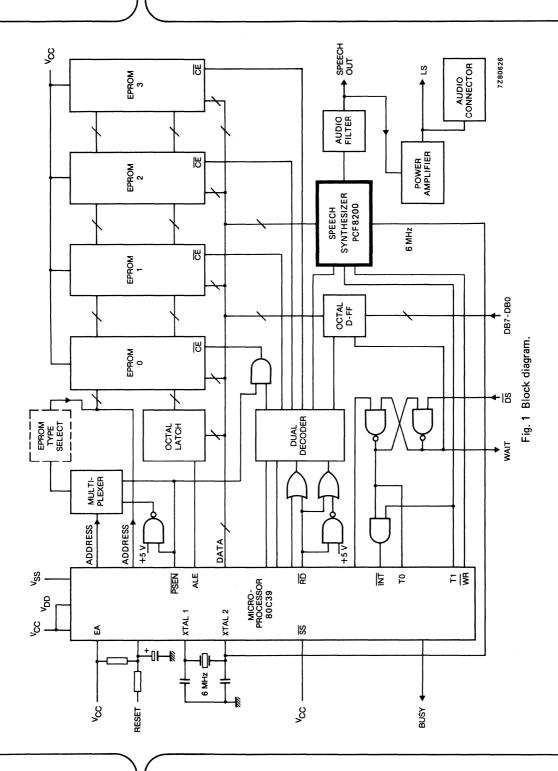

| PCF8200              | voice synthesizer (CMOS)                                                                                                                      | 1053         |

| PCF8566              | universal LCD driver for low multiplex rates (1:1 to 1:4) max. 96 segments                                                                    | 1145         |

| PCF8569              | LCD column driver for dot matrix graphic displays at multiplex rates of 1:8 or 1:16; 40 outputs                                               | 1151         |

| PCF8570/C            | 256 x 8-bit static RAM                                                                                                                        | 1159         |

| PCF8571              | 128 x 8-bit static RAM                                                                                                                        | 1159         |

| PCF8573              | clock/calendar                                                                                                                                | 1163         |

| PCF8574/A            | remote 8-bit I/O expander                                                                                                                     | 1179         |

| PCF8576              | universal LCD driver for low multiplex rates (1:1 to 1:4) max. 160 segments                                                                   | 1191         |

| PCF8577/A/C/CA       | LCD direct driver (32 segments) or duplex driver (64 segments)                                                                                | 1201         |

| PCF8578              | LCD row/column driver for dot matrix graphic displays; 40 outputs (24 are                                                                     | 1201         |

|                      | programmable)                                                                                                                                 |              |

| PCF8579              | LCD row/column driver for dot matrix graphic displays; 40 column outputs                                                                      | 1219         |

| PCF8581/C            | 128 x 8-bit static EEPROM; low-voltage                                                                                                        | 1229         |

| PCF8583              | clock/calender with 256 x 8-bit static RAM                                                                                                    | 1233         |

| PCF8591              | 8-bit ADC/DAC                                                                                                                                 | 1239         |

| UMA1000T             | data processor for cellular radio (DPROC)                                                                                                     | 1561         |

| UMA1010T             | low-power universal frequency synthesizer for radio communications; 400 MHz to 1150 MHz                                                       | 1591         |

| UMA1012T             | low-power universal frequency synthesizer for radio communications; 20 to 600 MHz                                                             | 1605         |

|                      | 333 111 12                                                                                                                                    |              |

| LISTENING-IN CIRCUIT |                                                                                                                                               |              |

| TEA1085              | listening-in circuit for line powered telephone sets; with anti-Larsen limiter                                                                | 1509         |

| MEMORIES             |                                                                                                                                               |              |

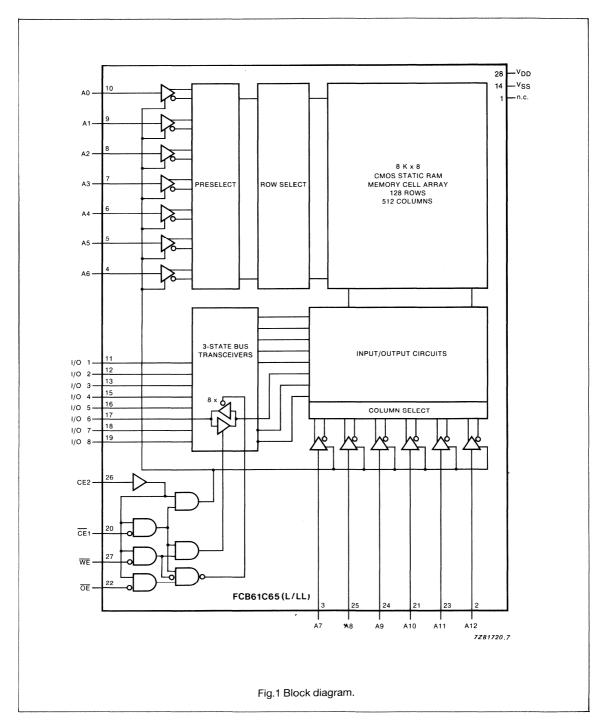

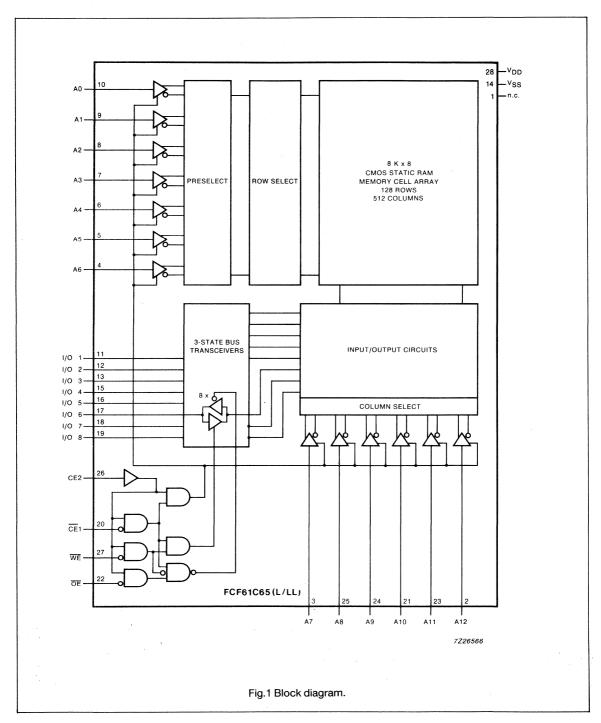

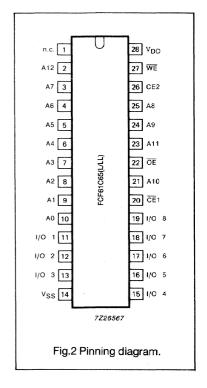

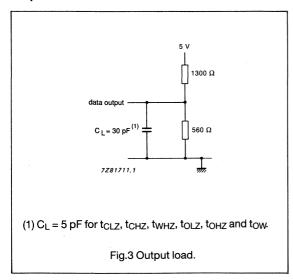

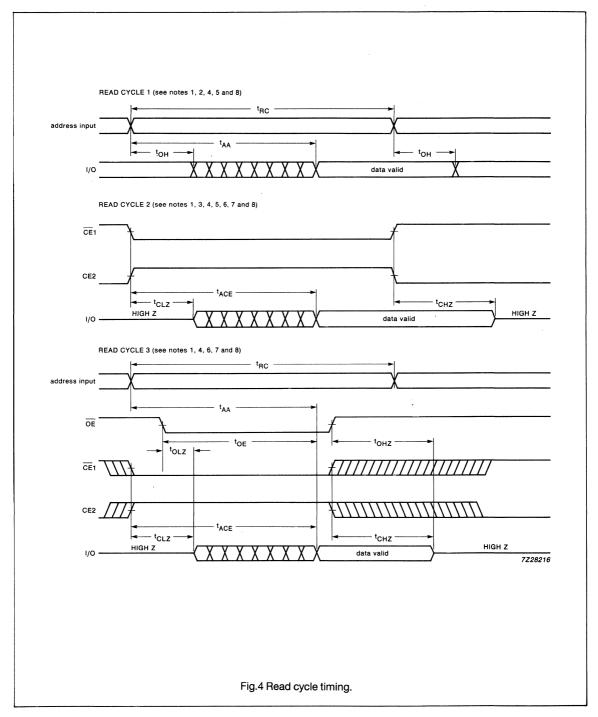

| FCB61C65 (L/LL)      | 8K x 8 high speed CMOS low-power static RAM; access time = 55 and 70 ns                                                                       | AE           |

| FCF61C65 (L/LL)      | 8K x 8 high speed CMOS low-power static RAM for extended temperature                                                                          | 45<br>55     |

| DC 9592 Eamily       | range; access time = 85 ns                                                                                                                    | 0.45         |

| PC.8582 Family       | 256 x 8-bit static EEPROM; CMOS; I <sup>2</sup> C-bus                                                                                         | 345          |

| PCD5101              | 256 x 4-bit static RAM                                                                                                                        | 997          |

| PCD5114              | 1024 x 4-bit static RAM                                                                                                                       | 1003         |

| PCF8570              | 256 x 8-bit static RAM; I <sup>2</sup> C-bus                                                                                                  | 1159         |

| PCF8570C             | 256 x 8-bit static RAM; I <sup>2</sup> C-bus; different slave address                                                                         | 1159         |

| PCF8571              | 128 x 8-bit static RAM; I <sup>2</sup> C-bus                                                                                                  | 1159         |

| PCF8581/C            | 128 x 8-bit static EEPROM; low-voltage; I <sup>2</sup> C-bus                                                                                  | 1229         |

| PCF8583              | clock/calendar with 256 x 8-bit static RAM; I <sup>2</sup> C-bus                                                                              | 1233         |

|                      |                                                                                                                                               |              |

## Functional index

| type number    | description                                                                                                                                                                                                                   | page       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| MICROCONTROLLE | RS                                                                                                                                                                                                                            |            |

| PCA80C552-4    | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C             | 435        |

| PCA80C562      | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C              | 449        |

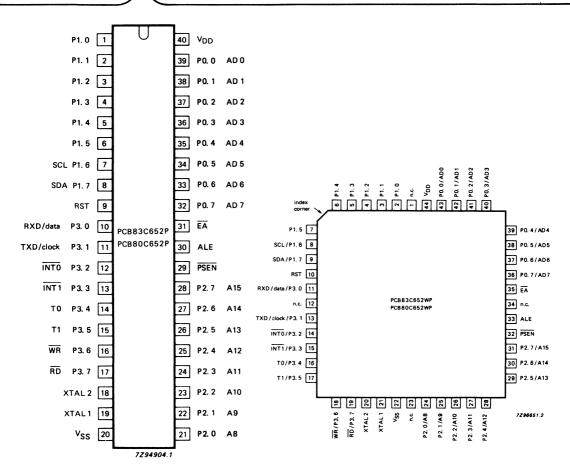

| PCA80C652      | 256 x 8 RAM; serial I/O; UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to +125 °C                                                                                                                                            | 463        |

| PCA83C552-4    | 256 x 8 RAM; 4K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C | 435        |

| PCA83C562      | 256 x 8 RAM; 8K x 8 ROM; 80C531 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C | 449        |

| PCA83C652      | 256 x 8 RAM; 8K x 8 ROM; serial I/O; ÚART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to +125 °C                                                                                                                                | 463        |

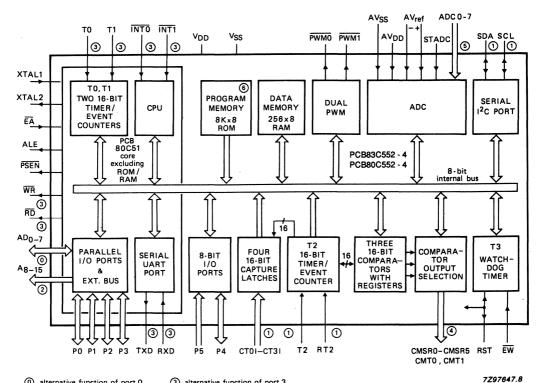

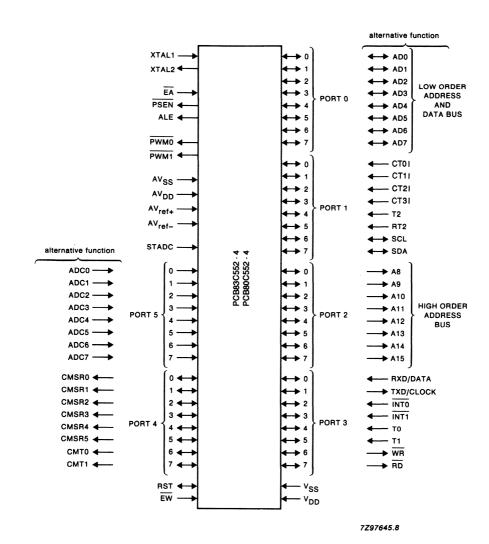

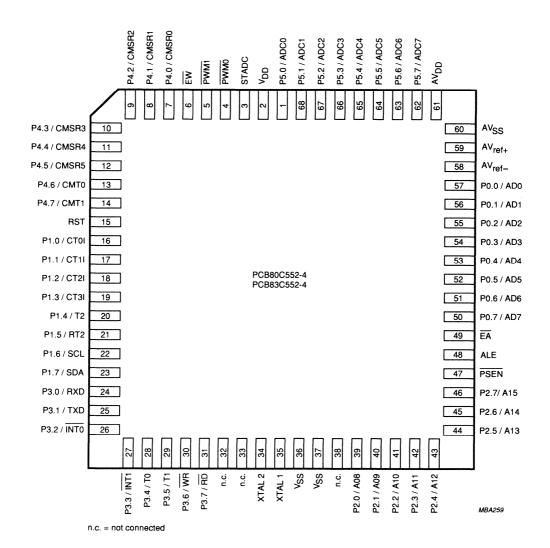

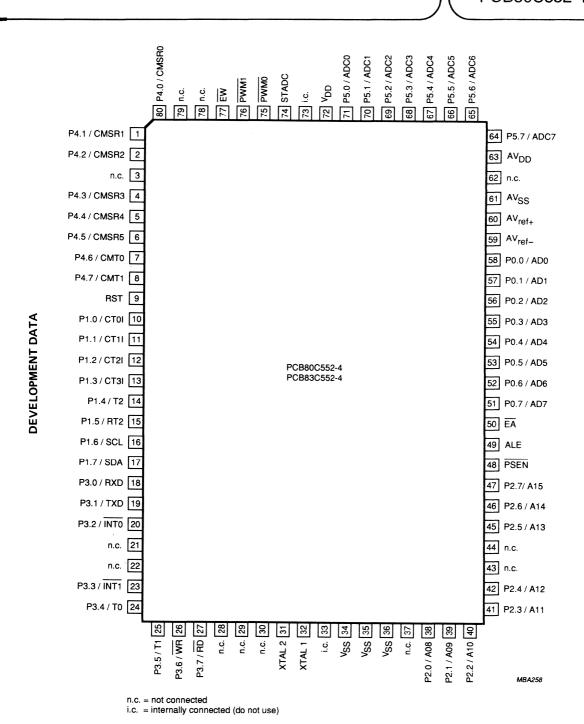

| PCB80C552-4    | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                | 435        |

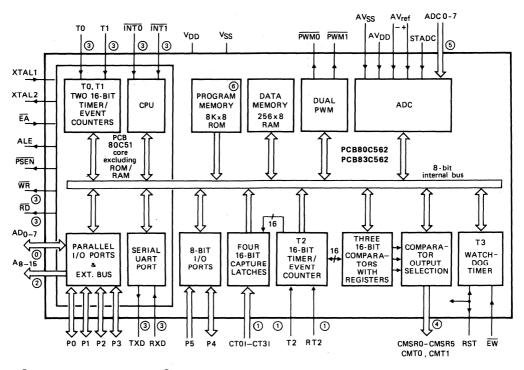

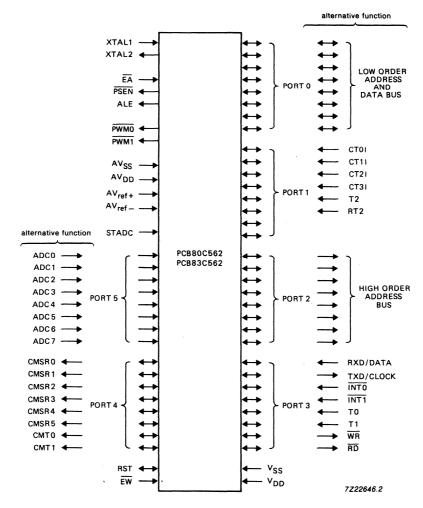

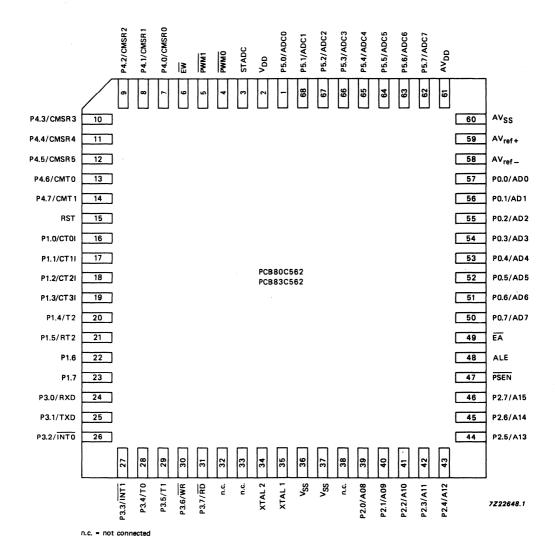

| PCB80C562      | 256 x 8 RAM; 80C531 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8                                                                                          | 449        |

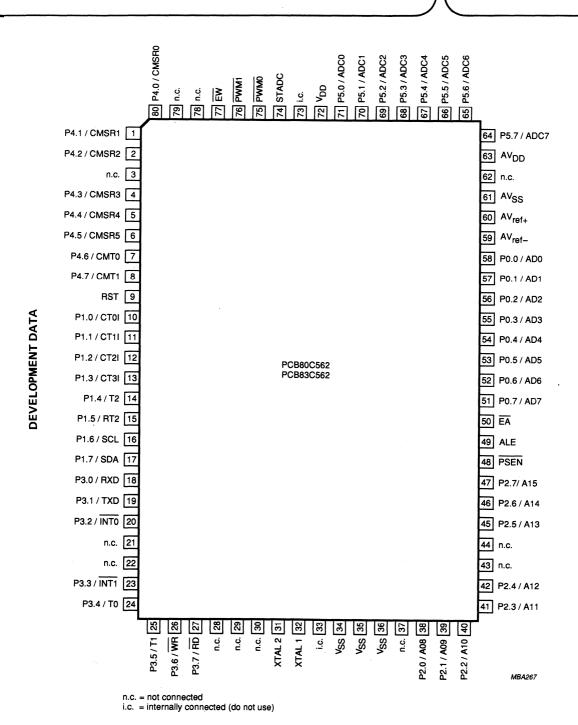

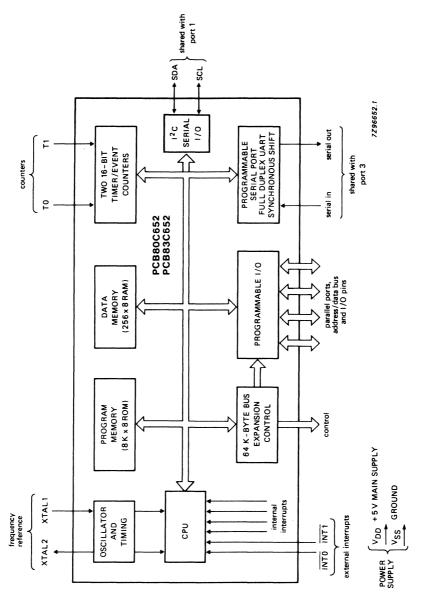

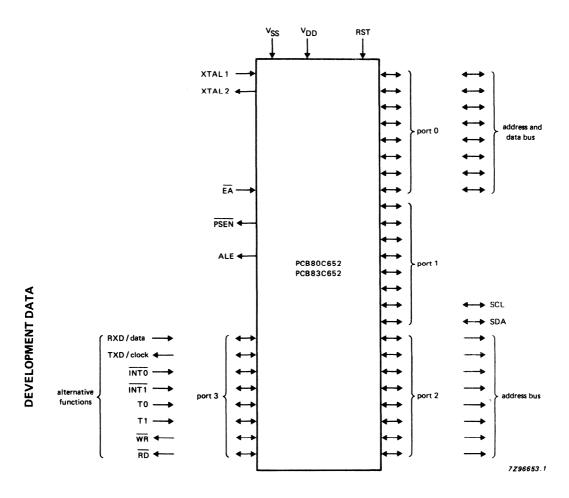

| PCB80C652      | multiplexed input lines; 1.2 to 12 MHz; $I^2$ C-bus; $-40$ to $+125$ $^{\circ}$ C 256 x 8 RAM; serial I/O; UART; $I^2$ C-bus; 1.2 to 12 MHz; 0 to $+70$ $^{\circ}$ C                                                          | 463        |

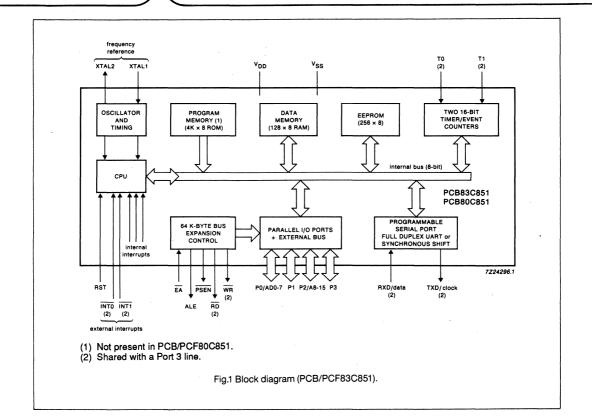

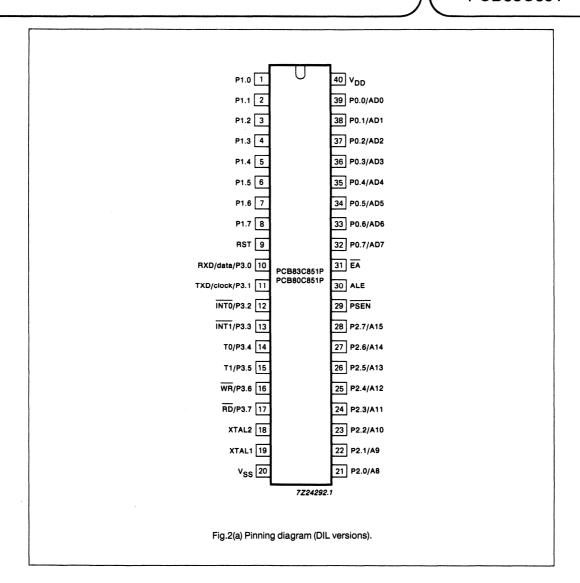

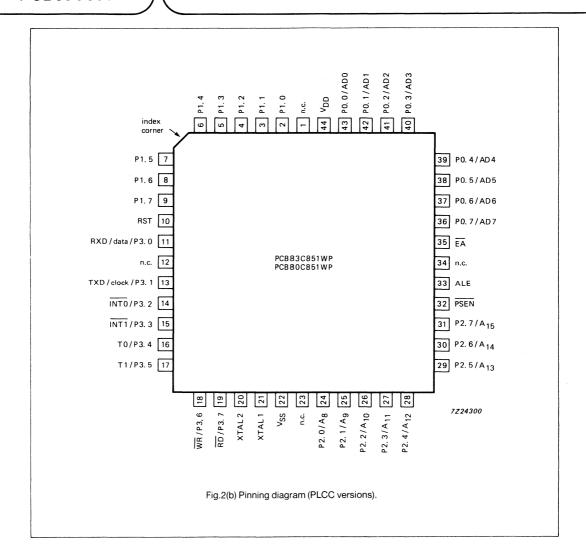

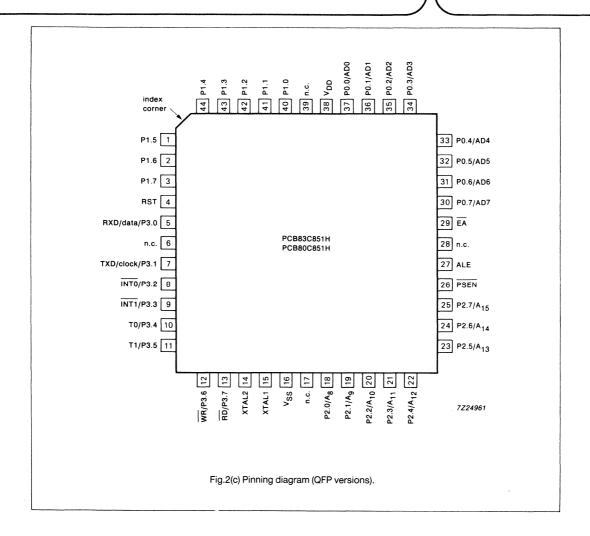

| PCB80C851      | 128 x 8 RAM; 256 x 8 EEPROM; 1.2 to 12 MHz;                                                                                                                                                                                   | 403<br>475 |

|                | 0 to +70 °C; special security mode                                                                                                                                                                                            |            |

| PCB83C552-4    | 256 x 8 RAM; 8K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C    | 435        |

| PCB83C562      | 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8                                                                               | 449        |

| PCB83C652      | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C<br>256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz;<br>0 to +70 °C                                                | 463        |

| PCB83C851      | 128 x 8 RAM; 4K x 8 ROM; 256 x 8 EEPROM; 1.2 to 12 MHz; 0 to +70 °C; special security mode                                                                                                                                    | 475        |

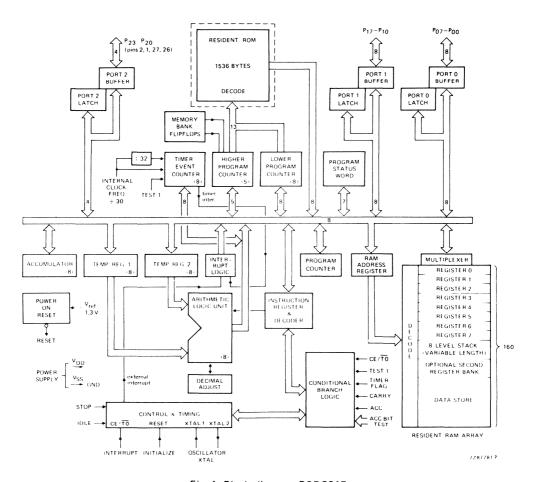

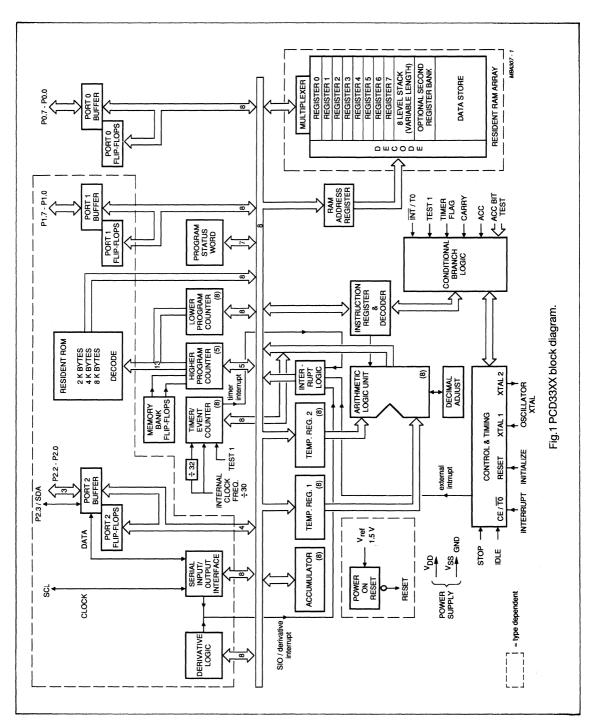

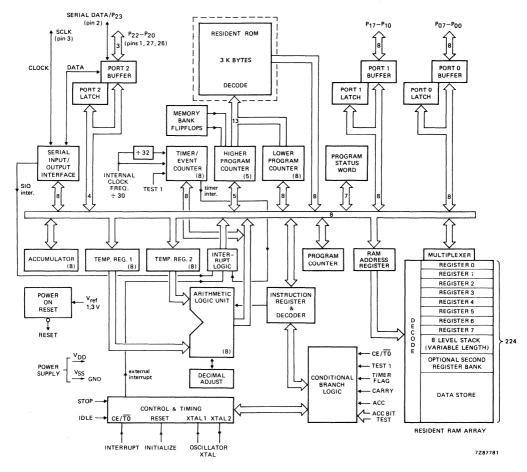

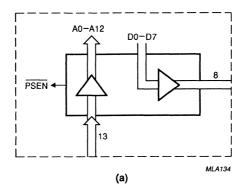

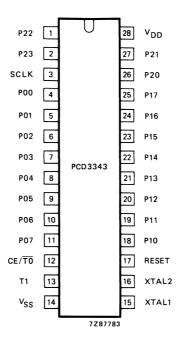

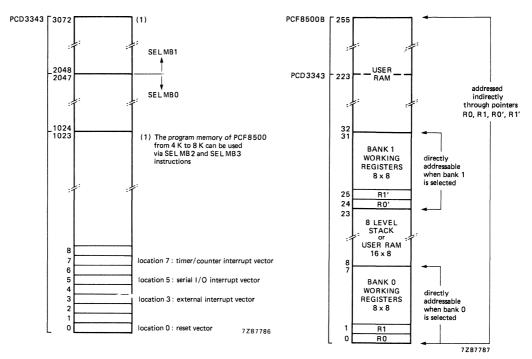

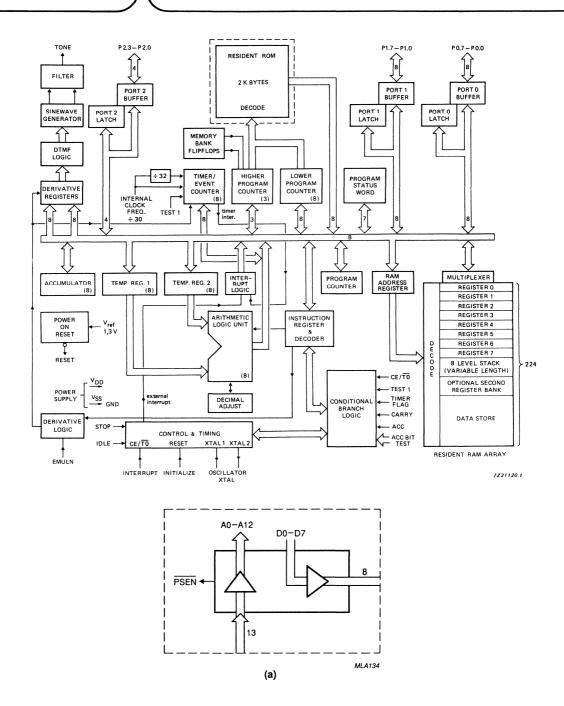

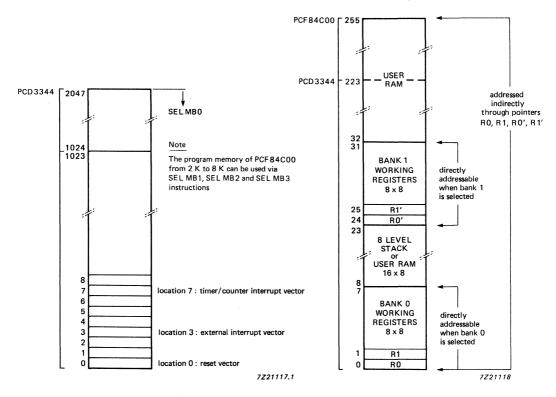

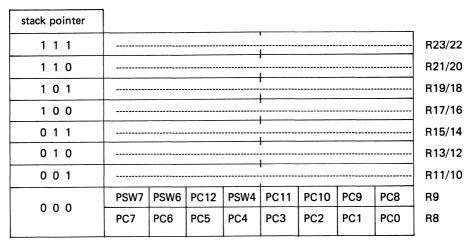

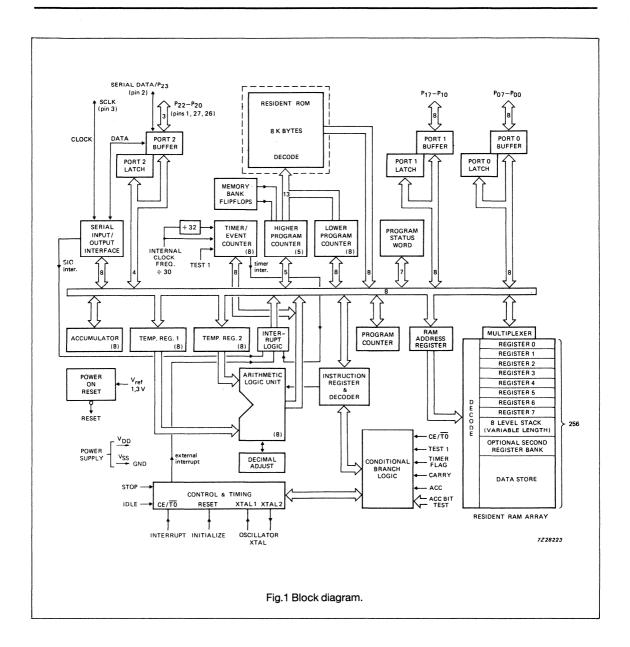

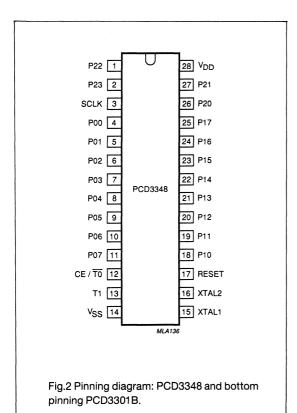

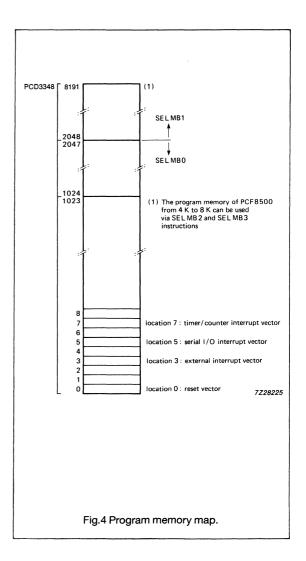

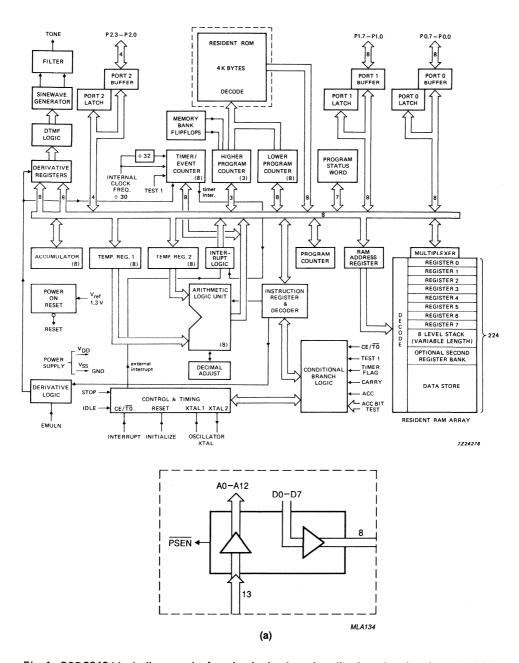

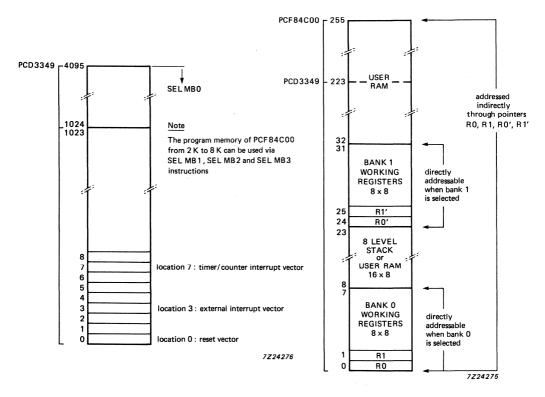

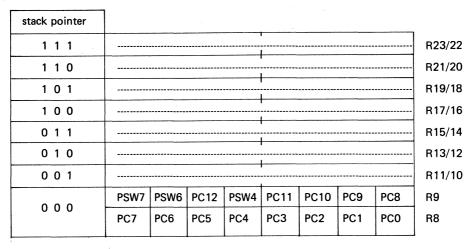

| PCD33XX Family | single-chip 8-bit microcontroller family specification                                                                                                                                                                        | 579        |

| PCD3315        | CMOS microcontroller for telephone sets; 160 x 8 RAM; 15K x 8 ROM; –25 to +70 °C                                                                                                                                              | 527        |

| PCD3343        | microcontroller for telephone sets; 224 x 8 RAM; 3K x 8 ROM; 20 I/O lines; I <sup>2</sup> C-bus                                                                                                                               | 615        |

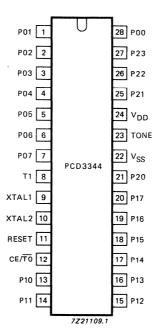

| PCD3344        | CMOS microcontroller with on-chip DTMF generator; 224 x 8 RAM; 2K x 8 ROM; 20 I/O lines                                                                                                                                       | 655        |

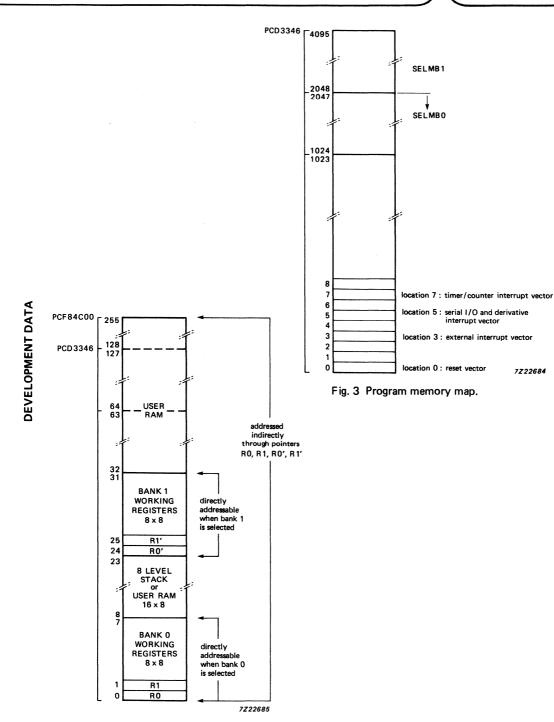

| PCD3346        | microcontroller for telephone sets; 128 x 8 RAM; 4K x 8 ROM; 256 x 8 EEPROM; 20 I/O lines; I <sup>2</sup> C-bus                                                                                                               | 691        |

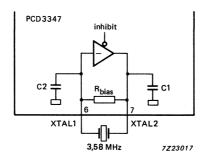

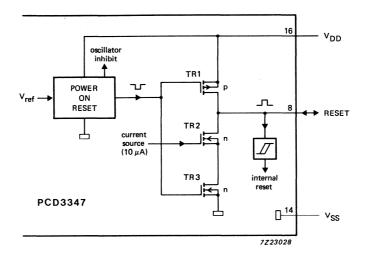

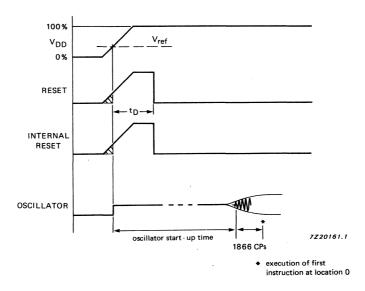

| PCD3347        | CMOS microcontroller with on-chip DTMF generator; 64 x 8 RAM; 1.5K x 8 ROM: 12 I/O lines                                                                                                                                      | 741        |

## Functional index

| type number                                                         | description                                                                                                                                                                                                                                                                                                                                                                      | page                                 |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| PCD3348                                                             | CMOS microcontroller for telephone sets; 256 x 8 RAM; 8K x 8 ROM;                                                                                                                                                                                                                                                                                                                | 777                                  |

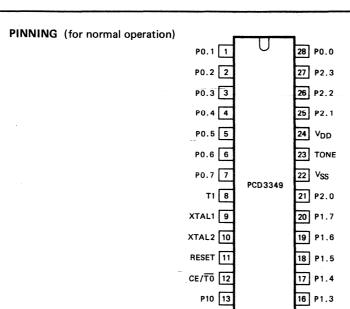

| PCD3349                                                             | 20 I/O lines; I <sup>2</sup> C-bus<br>CMOS microcontroller with on-chip DTMF generator; 224 x 8 RAM; 4K x 8<br>ROM; 20 I/O lines                                                                                                                                                                                                                                                 | 817                                  |

| PCF80C552-4                                                         | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +85 °C                                                                                                                                                                 | 435                                  |

| PCF80C562                                                           | watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +85 °C                                                                                                                                                                                                                                    | 449                                  |

| PCF80C652<br>PCF80C851                                              | 256 x 8 RAM; serial I/O; UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to +85 °C<br>128 x 8 RAM; 256 x 8 EEPROM; 1.2 to 12 MHz; -40 to +85 °C                                                                                                                                                                                                                                   | 463<br>475                           |

| PCF83C552-4                                                         | 256 x 8 RAM; 8K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +85 °C                                                                                                                                                     | 435                                  |

| PCF83C562                                                           | 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2 pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +85 °C                                                                                                                                                      | 449                                  |

| PCF83C652                                                           | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to +85 °C                                                                                                                                                                                                                                                                                    | 463                                  |

| PCF83C851<br>PCF84CXXX Family<br>PCF84C00<br>PCF84C12<br>PCF84C21/C | 128 x 8 RAM; 4K x 8 ROM; 256 x 8 EEPROM; 1.2 to 12 MHz; -40 to +85 °C single-chip 8-bit microcontroller family specification; I <sup>2</sup> C-bus 256 x 8 RAM; bond-out version of PCF84CXX family; I <sup>2</sup> C-bus low cost microcontroller; 64 x 8 RAM; 1K x 8 ROM 64 x 8 RAM; 2K x 8 ROM; plus 8-bit LED driver; I <sup>2</sup> C-bus; -40 to +85 °C                    | 475<br>1067<br>1103<br>1111<br>1103  |

| PCF84C22<br>PCF84C41/C<br>PCF84C42<br>PCF84C81/C<br>PCF84C85        | low cost microcontroller; 64 x 8 RAM; 1K x 8 ROM<br>128 x 8 RAM; 4K x 8 ROM; plus 8-bit LED driver; l <sup>2</sup> C-bus; -40 to +85 °C<br>low cost microcontroller; 64 x 8 RAM; 4K x 8 ROM<br>256 x 8 RAM; 8K x 8 ROM; plus 8-bit LED driver; l <sup>2</sup> C-bus; -40 to +85 °C<br>256 x 8 RAM; 8K x 8 ROM; 32 l/O lines; plus 8-bit LED driver; l <sup>2</sup> C-bus; -40 to | 1111<br>1103<br>1111<br>1103<br>1115 |

| PCF84C121                                                           | +85 °C microcontroller; 64 x 8 RAM; 1K x 8 ROM; 8 x 8 EEPROM; 100 kHz to                                                                                                                                                                                                                                                                                                         | 1121                                 |

| PCF84C230                                                           | 10 MHz; 13 I/O lines; 8-bit CPU; -40 to +85 °C<br>microcontroller; 64 x 8 RAM; 2K x 8 ROM; 8-bit CPU; 12 I/O lines;<br>LCD driver; CMOS: -40 to +85 °C                                                                                                                                                                                                                           | 1127                                 |

| PCF84C633A                                                          | 256 x 8 RAM; 6K x 8 ROM; 28 I/O lines; plus LCD driver; derivative port; timer/capture and timer/counter                                                                                                                                                                                                                                                                         | 1133                                 |

| PCF84C853A                                                          | 256 x 8 RAM; 8K x 8 ROM; 33 I/O lines; plus LCD driver; derivative port; timer/capture and timer/counter                                                                                                                                                                                                                                                                         | 1139                                 |

| PCF86C410                                                           | microcontroller; 128 x 8 RAM; 4K x 8 ROM; 32 I/O lines; 32 kHz to 16 MHz; 2 x 16-bit timer/event counter; –40 to +85°C; I <sup>2</sup> C-bus                                                                                                                                                                                                                                     | 1257                                 |

| PCF86C610                                                           | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 32 I/O lines; 32 kHz to 16 MHz; 2 x 16-bit timer/event counter: –40 to +85°C: I <sup>2</sup> C-bus                                                                                                                                                                                                                                     | 1257                                 |

April 1991

# Functional index

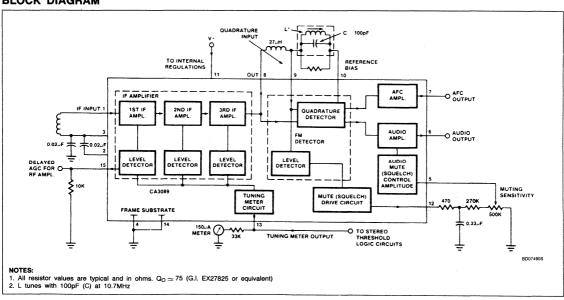

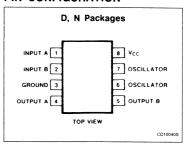

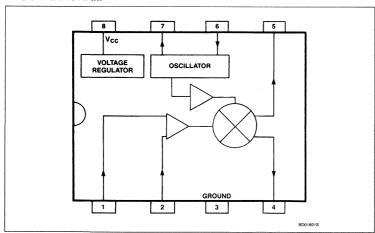

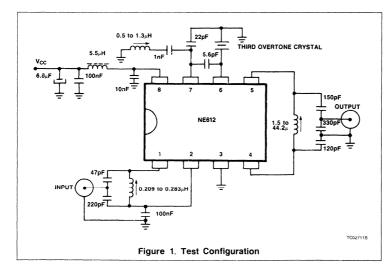

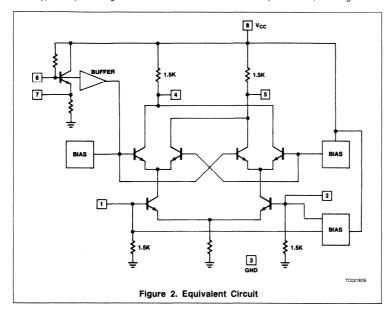

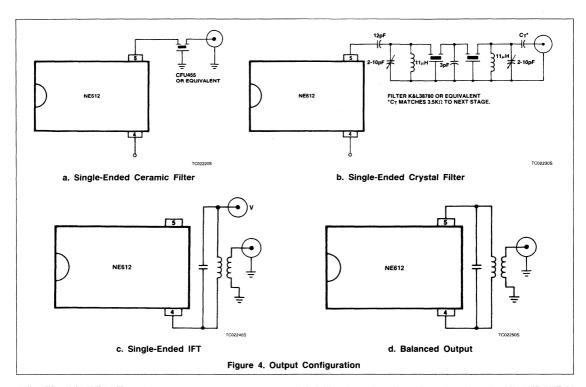

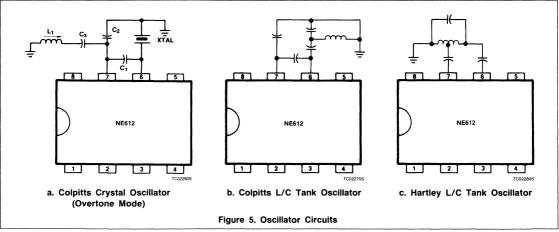

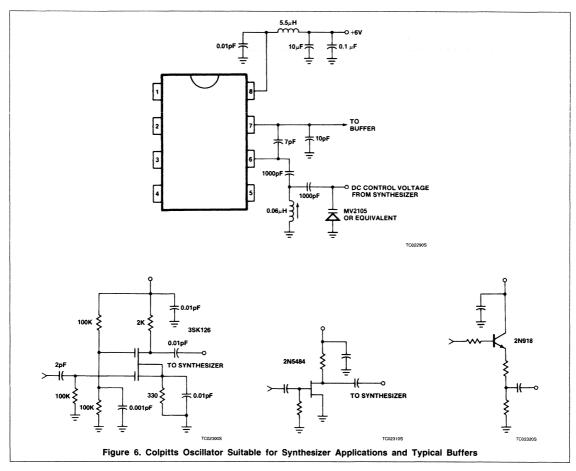

| MIXERS AND OSCILL                                                                                                        | ATORS/IF SYSTEMS                                                                                                                                                                                                                                                                                                                                                  |                                                                          |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

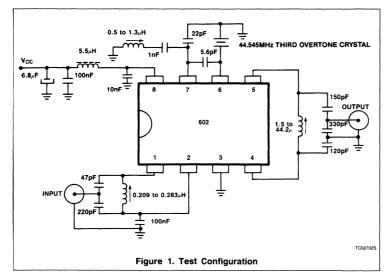

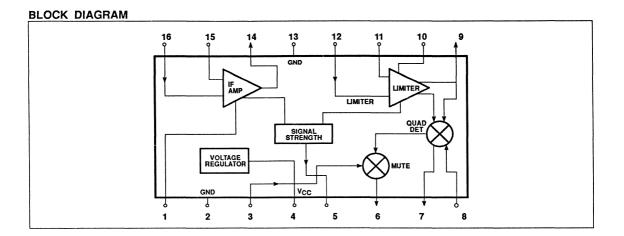

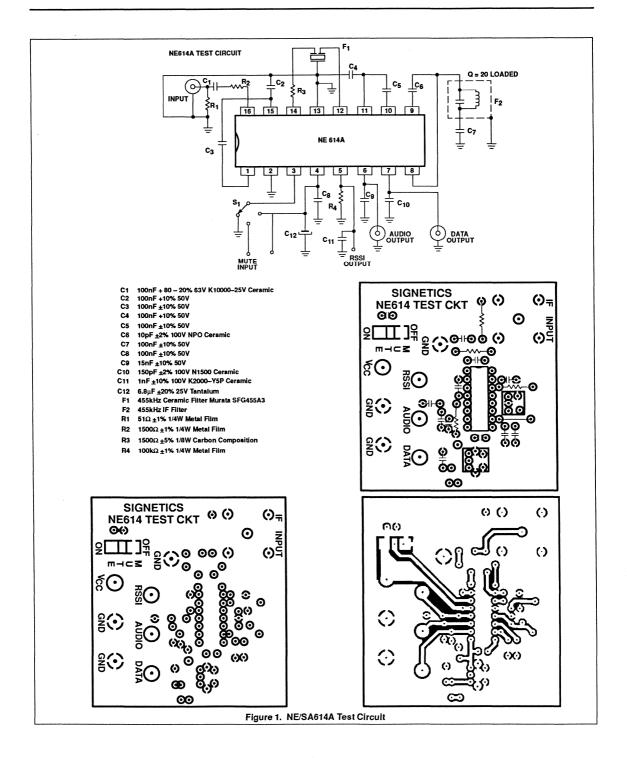

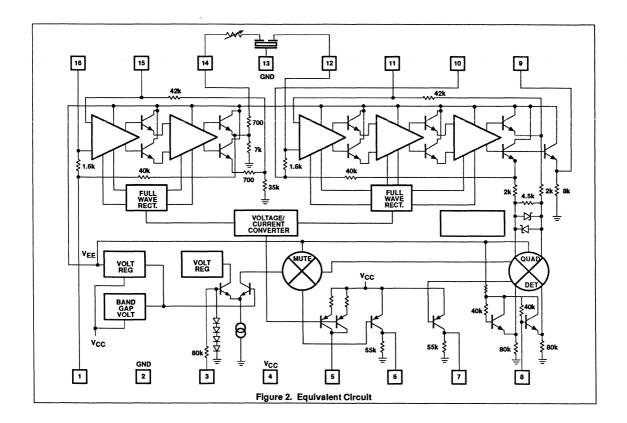

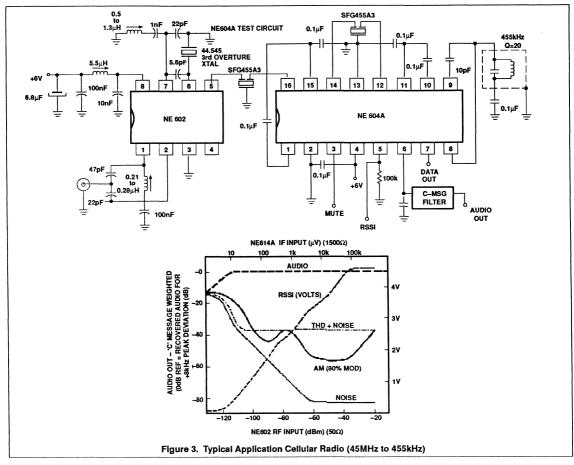

| CA3089<br>MC3361<br>NE/SA602<br>NE/SA602A<br>NE/SA604A<br>NE/SA605<br>NE612<br>NE614<br>NE/SA614A<br>NE/SA615<br>TDA1576 | FM IF system low-power FM IF system double-balanced mixer and oscillator double-balanced mixer and oscillator high-performance low-power FM IF system high-performance low-power mixer FM IF system double-balanced mixer and oscillator low-power FM IF system low-power FM IF system high-performance low-power mixer FM IF system FM/IF amplifier and detector | 39<br>65<br>161<br>167<br>175<br>185<br>195<br>201<br>211<br>221<br>1293 |

| PAGING DECODERS                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |

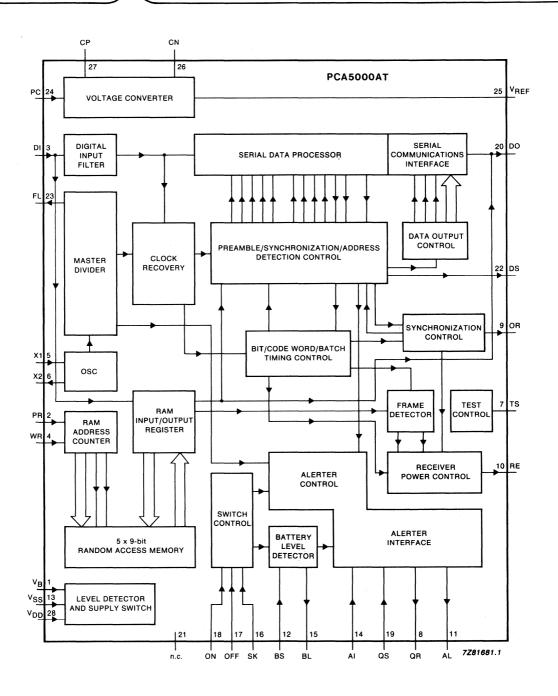

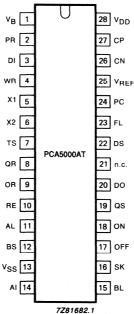

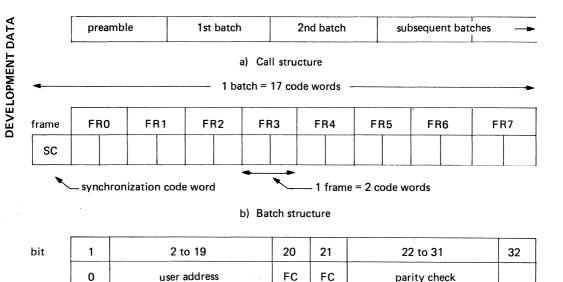

| PCA5000AT                                                                                                                | decoder for POCSAG paging systems                                                                                                                                                                                                                                                                                                                                 | 359                                                                      |

| PAGING RECEIVERS<br>UAA2033T<br>UAA2050T                                                                                 | low-power digital VHF paging receiver<br>low-power digital UHF paging receiver                                                                                                                                                                                                                                                                                    | 1535<br>1543                                                             |

| PHASE-LOCKED LOC                                                                                                         | OPS .                                                                                                                                                                                                                                                                                                                                                             |                                                                          |

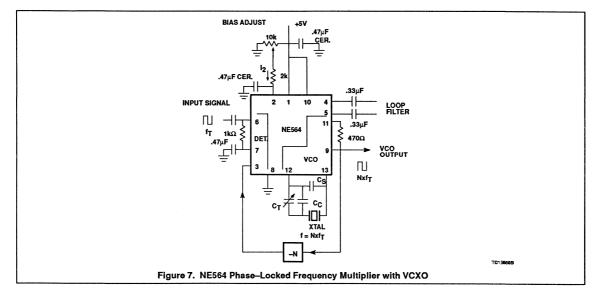

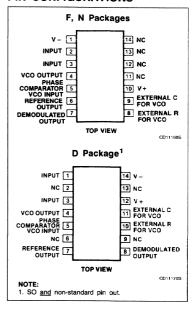

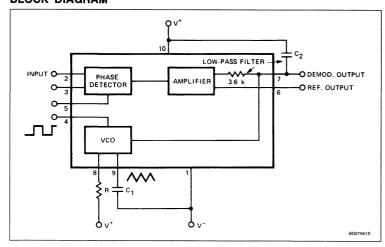

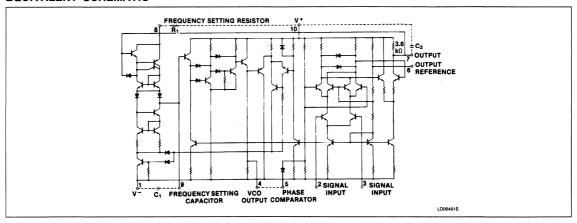

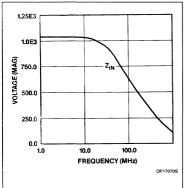

| NE/SE564<br>NE/SE565<br>NE/SE566<br>NE/SE567<br>NE568<br>74HC/HCT297<br>74HC/HCT4046A<br>74HC/HCT7046A                   | phase-locked loop 0.001 Hz to 500 kHz phase-locked loop function generator tone decoder/phase-locked loop 150 MHz phase-locked loop digital phase-locked loop filter phase-locked loop with VCO phase-locked loop with VCO                                                                                                                                        | 73<br>83<br>89<br>95<br>107<br>1619<br>1627<br>1655                      |

| POWER CONTROL IC                                                                                                         | es<br>S                                                                                                                                                                                                                                                                                                                                                           |                                                                          |

| PCF1251<br>PCF1252-X Family<br>TEA1081                                                                                   | micropower DC voltage detector<br>power-fail detector and reset generator; trip voltage = 2.55 to 4.75 V<br>supply circuit with power-down for telephone set peripherals                                                                                                                                                                                          | 1009<br>1013<br>1499                                                     |

| SPEECH TRANSMISS                                                                                                         | SION                                                                                                                                                                                                                                                                                                                                                              |                                                                          |

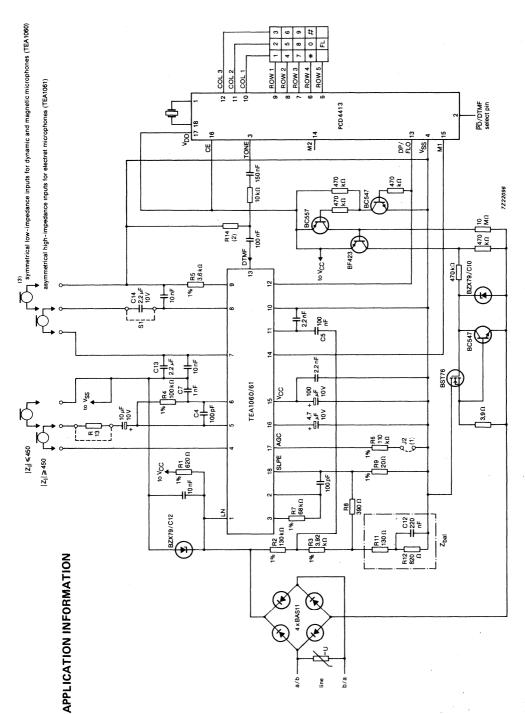

| TEA1060                                                                                                                  | speech/transmission circuit with dialler interface; low impedance input for dynamic and magnetic microphones                                                                                                                                                                                                                                                      | 1349                                                                     |

| TEA1061                                                                                                                  | speech/transmission circuit with dialler interface; high impedance input for electret and piezo-eletric microphones                                                                                                                                                                                                                                               | 1349                                                                     |

| TEA1062                                                                                                                  | low-voltage speech/transmission circuit with dialler interface for lower performance high volume markets; suitable for parallel operation                                                                                                                                                                                                                         | 1365                                                                     |

| TEA1063                                                                                                                  | low-voltage speech circuit with dialler interface and speech-controlled transmit level dynamic limiting; (special markets)                                                                                                                                                                                                                                        | 1385                                                                     |

| TEA1064A                                                                                                                 | speech/transmission circuit with dialler interface and transmit level dynamic limiting                                                                                                                                                                                                                                                                            | 1413                                                                     |

| TEA1066T                                                                                                                 | speech/transmission circuit with dialler interface                                                                                                                                                                                                                                                                                                                | 1441                                                                     |

| TEA1067                                                                                                                  | low-voltage speech/transmission circuit with dialler interface; input suitable for all microphone types                                                                                                                                                                                                                                                           | 1459                                                                     |

| TEA1068                                                                                                                  | speech/transmission circuit with dialler interface; input suitable for all microphone types                                                                                                                                                                                                                                                                       | 1479                                                                     |

| TONE RINGERS                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |

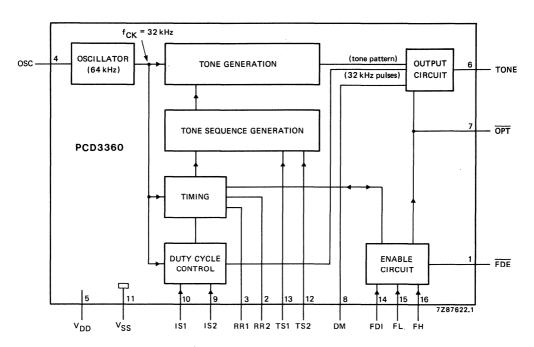

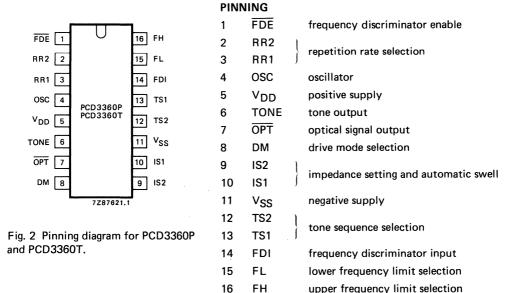

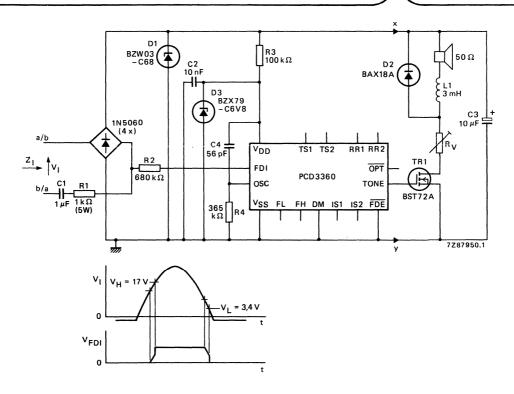

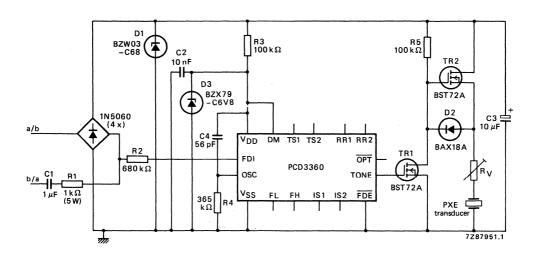

| PCD3360                                                                                                                  | programmable multi-tone ringer                                                                                                                                                                                                                                                                                                                                    | 853                                                                      |

## Functional index

#### **VOICE SYNTHESIZERS**

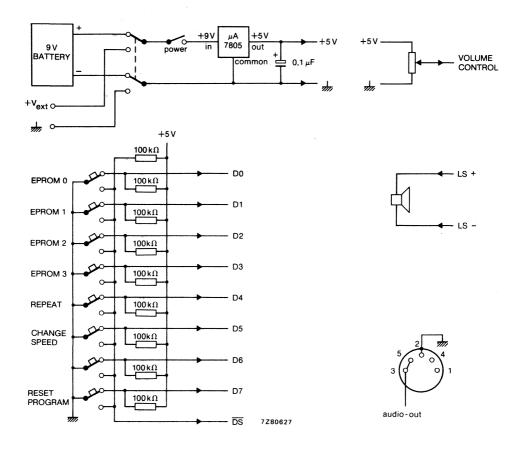

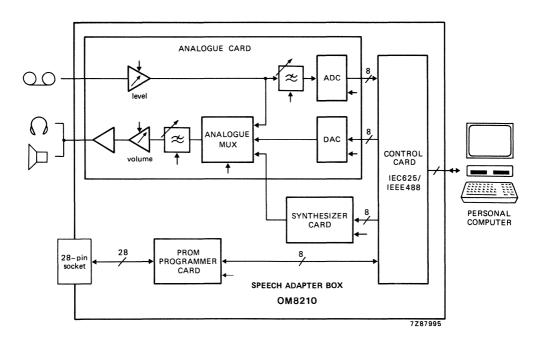

| OM8200  | speech demonstration board (PCF8200)           | 333  |

|---------|------------------------------------------------|------|

| OM8201  | speech demonstration box (PCF8200)             | 337  |

| OM8209  | update package for OM8010                      | 339  |

| OM8210  | speech analysis/editing system (PCF8200)       | 341  |

| PCF8200 | voice synthesizer (CMOS); I <sup>2</sup> C-bus | 1053 |

## Numerical index

#### **NUMERICAL INDEX**

| type number                                                                  | description                                                                                                                                                                                                                                                        | page                            |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| CA3089N<br>FCB61C65 (L/LL)-XXP<br>FCB61C65 (L/LL)-XXT<br>FCF61C65 (L/LL)-85T | FM IF system 8 K x 8 high speed CMOS low-power static RAM; access time = 55 and 70 ns 8 K x 8 high speed CMOS low-power static RAM; access time = 55 and 70 ns 8 K x 8 high speed CMOS low-power static RAM for extended temperature                               | 39<br>45<br>45<br>55            |

| MC3361D                                                                      | range; access time = 85 ns<br>low-power FM IF system                                                                                                                                                                                                               | 65                              |

| MC3361N<br>NE542N<br>NE564D<br>NE564N<br>NE565D                              | low-power FM IF system<br>dual low-noise preamplifier<br>phase-locked loop<br>phase-locked loop<br>0.001 Hz to 500 kHz phase-locked loop                                                                                                                           | 65<br>69<br>73<br>73<br>83      |

| NE565F<br>NE565N<br>NE566D<br>NE566F<br>NE566N                               | 0.001 Hz to 500 kHz phase-locked loop<br>0.001 Hz to 500 kHz phase-locked loop<br>function generator<br>function generator<br>function generator                                                                                                                   | 83<br>83<br>89<br>89            |

| NE567D<br>NE567F<br>NE567FE<br>NE567N<br>NE568D                              | tone decoder/phase-locked loop<br>tone decoder/phase-locked loop<br>tone decoder/phase-locked loop<br>tone decoder/phase-locked loop<br>150 MHz phase-locked loop                                                                                                  | 95<br>95<br>95<br>95<br>107     |

| NE568N<br>NE570F<br>NE570N<br>NE571D<br>NE571F                               | 150 MHz phase-locked loop<br>compandor<br>compandor<br>compandor<br>compandor                                                                                                                                                                                      | 107<br>113<br>113<br>113<br>113 |

| NE571N<br>NE572D<br>NE572N<br>NE575D<br>NE575N                               | compandor programmable analog compandor programmable analog compandor low-voltage compandor low-voltage compandor                                                                                                                                                  | 113<br>123<br>123<br>131<br>131 |

| NE575DJ<br>NE577D<br>NE577N<br>NE578D<br>NE578N                              | low-voltage compandor in very small outline package (VSOP) unity gain level programmable low-power compandor | 143<br>153<br>153<br>157<br>157 |

| NE602D<br>NE602N<br>NE602FE<br>NE602AD<br>NE602AN                            | double-balanced mixer and oscillator<br>double-balanced mixer and oscillator<br>double-balanced mixer and oscillator<br>double-balanced mixer and oscillator<br>double-balanced mixer and oscillator                                                               | 161<br>161<br>161<br>167<br>167 |

| NE602AFE<br>NE604AD<br>NE604AN<br>NE605D                                     | double-balanced mixer and oscillator<br>high-performance low-power FM IF system<br>high-performance low-power FM IF system<br>high-performance low-power mixer FM IF system                                                                                        | 167<br>175<br>175<br>185        |

# **Numerical** index

| type number   | description                                                                  | page |

|---------------|------------------------------------------------------------------------------|------|

| NE605N        | high-performance low-power mixer FM IF system                                | 185  |

| NE612D        | double-balanced mixer and oscillator                                         | 195  |

| NE612N        | double-balanced mixer and oscillator                                         | 195  |

| NE614D        | low-power FM IF system                                                       | 201  |

| NE614N        | low-power FM IF system                                                       | 201  |

| NE614AD       | low-power FM IF system                                                       | 211  |

| NE614AN       | low-power FM IF system                                                       | 211  |

| NE615D        | high-performance low-power mixer FM IF system                                | 221  |

| NE615N        | high-performance low-power mixer FM IF system                                | 221  |

| NE5204D       | wideband high-frequency amplifier                                            | 231  |

| NE5204N       | wideband high-frequency amplifier                                            | 231  |

| NE5205D       | wideband high-frequency amplifier                                            | 241  |

| NE5205EC      | wideband high-frequency amplifier                                            | 241  |

| NE5205FE      | wideband high-frequency amplifier                                            | 241  |

| NE5205N       | wideband high-frequency amplifier                                            | 241  |

| NE5209D       | wideband variable gain amplifier                                             | 253  |

| NE5209N       | wideband variable gain amplifier                                             | 253  |

| NE5230D       | low-voltage operational amplifier                                            | 267  |

| NE5230FE      | low-voltage operational amplifier                                            | 267  |

| NE5230N       | low-voltage operational amplifier                                            | 267  |

| NE5234D       | matched quad high-performance low-voltage operational amplifier              | 279  |

| NE5234N       | matched quad high-performance low-voltage operational amplifier              | 279  |

| NE5539D       | high-frequency operational amplifier                                         | 285  |

| NE5539F       | high-frequency operational amplifier                                         | 285  |

| NE5539N       | high-frequency operational amplifier                                         | 285  |

| NE5750D       | audio processor - companding and amplifier section                           | 293  |

| NE5750N       | audio processor - companding and amplifier section                           | 293  |

| NE5751D       | audio processor - filter and control section                                 | 301  |

| NE5751N       | audio processor - filter and control section                                 | 301  |

| NE5900D       | call progress decoder                                                        | 311  |

| NE5900N       | call progress decoder                                                        | 311  |

|               |                                                                              |      |

| OM1036CP      | dialler circuit with redial                                                  | 319  |

| OM8200        | speech demonstration board (PCF8200)                                         | 333  |

| OM8201        | speech demonstration box (PCF8200)                                           | 337  |

| OM8209        | update package for OM8010                                                    | 339  |

| OM8210        | speech analysis/editing system (PCF8200)                                     | 341  |

| PCA5000AT     | decoder for POCSAG paging systems                                            | 359  |

| PCA80C552-4WP | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter;            | 435  |

|               | watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with 8           |      |

| PCA80C552-4H  | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter;            | 435  |

|               | watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with 8           |      |

|               | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C |      |

| PCA80C562WP   | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter;            | 449  |

|               | watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8            |      |

|               | multiplexed input lines: 1.2 to 12 MHz: I <sup>2</sup> C-bus: -40 to +125 °C |      |

## Numerical index

| type number     | description                                                                                                                                                                                                      | page |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| PCA80C562H      | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C | 449  |

| PCA80C652P      | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C                                                                                                                               | 463  |

| PCA80C652WP     | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C                                                                                                                               | 463  |

| PCA80C652H      | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                                                                               | 463  |

| PCA83C552-4WP   | 256 x 8 RAM; 4K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/<br>counter; watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with                                                               | 435  |

|                 | 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                                                                                   |      |

| PCA83C552-4H    | 256 x 8 RAM; 4K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with                                                                   | 435  |

| DO A COOFFICIAL | 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C                                                                                                                                   |      |

| PCA83C562H      | 256 x 8 RAM; 8K x 8 ROM; 80C531 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8                                                                 | 449  |

| DC A SOCECOLAID | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                                                                                     | 440  |

| PCA83C562WP     | 256 x 8 RAM; 8K x 8 ROM; 80C531 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8                                                                 | 449  |

| DO 4 000050D    | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C                                                                                                                                     | 400  |

| PCA83C652P      | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                                                                   | 463  |

| PCA83C652H      | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 $^{\circ}$ C                                                                                                         | 463  |

| PCA83C652WP     | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; -40 to +125 °C                                                                                                                   | 463  |

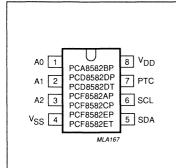

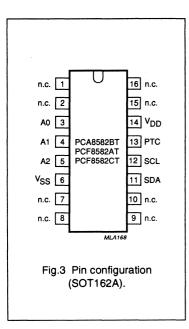

| PCA8582BP       | 256 x 8-bit static EEPROM; CMOS; I <sup>2</sup> C-bus; for automotive applications                                                                                                                               | 345  |

| PCA8582BT       | 256 x 8-bit static EEPROM; CMOS; I <sup>2</sup> C-bus; for automotive applications                                                                                                                               | 345  |

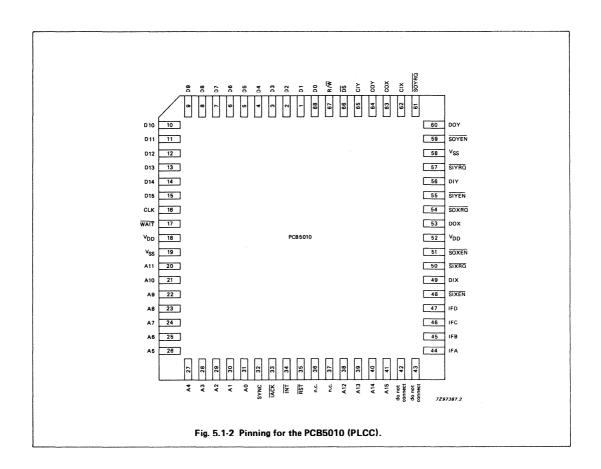

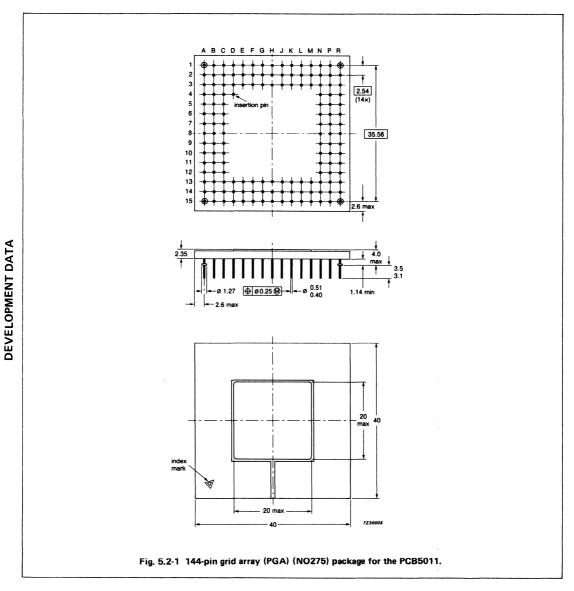

| PCB5010WP-8     | single-chip digital signal processor                                                                                                                                                                             | 379  |

| PCB5011YC-8     | ROM-less version of PCB5010                                                                                                                                                                                      | 379  |

| PCB80C552-4WP   | 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with 8                                                                             | 435  |

| PCB80C552-4H    | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C 256 x 8 RAM; 80C31 CPU plus 16-bit capture/compare timer/counter;                                                                      | 435  |

| 1 00000332-411  | watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                                                                     | 435  |

| PCB80C562WP     | 256 x 8 RAM; 80C531 CPU plus 16-bit capture/compare timer/counter;                                                                                                                                               | 449  |

| . 0200002771    | watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                   | ,,,, |

| PCB80C562H      | 256 x 8 RAM; 80C531 CPU plus 16-bit capture/compare timer/counter;                                                                                                                                               | 449  |

| 1 0500030211    | watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C                                                                   | 443  |

| PCB80C652P      | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                                                                                                                                  | 463  |

| PCB80C652H      | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                                                                                                                                  | 463  |

| PCB80C652WP     | 256 x 8 RAM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                                                                                                                                  | 463  |

| PCB80C851P      | 128 x 8 RAM; 256 x 8 EEPROM; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C; special security mode                                                                                                             | 475  |

| PCB80C851H      | 128 x 8 RAM; 256 x 8 EEPROM; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C; special security mode                                                                                                             | 475  |

# **Numerical** index

| type number   | description                                                                                                                                                                                                                  | page |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| PCB80C851WP   | 128 x 8 RAM; 256 x 8 EEPROM; 1.2 to 12 MHz; l <sup>2</sup> C-bus; 0 to +70 °C; special security mode                                                                                                                         | 475  |

| PCB83C552-4WP | 256 x 8 RAM; 8K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with                                                                               | 435  |

| PCB83C552-4H  | 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C 256 x 8 RAM; 8K x 8 ROM; 80C31 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 10-bit ADC with   | 435  |

| PCB83C562H    | 8 multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8  | 449  |

| PCB83C562WP   | multiplexed input lines; 1.2 to 12 MHz; I <sup>2</sup> C-bus; –40 to +125 °C 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU plus 16-bit capture/compare timer/counter; watchdog timer; 2-pulse-width modulated signals; 8-bit ADC with 8 | 449  |

| PCB83C652P    | multiplexed input lines; 1.2 to 12 MHz; $l^2$ C-bus; $-40$ to $+125$ °C 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; $l^2$ C-bus; 0 to $+70$ °C                                                                 | 463  |

| PCB83C652H    | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus; 0 to +70 °C                                                                                                                                  | 463  |

| PCB83C652WP   | 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART; 1.2 to 12 MHz; I <sup>2</sup> C-bus;                                                                                                                                              | 463  |

| PCB83C851P    | 0 to +70 °C<br>128 x 8 RAM; 4K X 8 ROM; 256 x 8 EEPROM; 1.2 to 12 MHz; I <sup>2</sup> C-bus;                                                                                                                                 | 475  |

| PCB83C851H    | 0 to +70 °C; special security mode<br>128 x 8 RAM; 4K X 8 ROM; 256 x 8 EEPROM; 1.2 to 12 MHz; I <sup>2</sup> C-bus;                                                                                                          | 475  |

| PCB83C851WP   | 0 to +70 °C; special security mode<br>128 x 8 RAM; 4K X 8 ROM; 256 x 8 EEPROM; 1.2 to 12 MHz; I <sup>2</sup> C-bus;<br>0 to +70 °C; special security mode                                                                    | 475  |

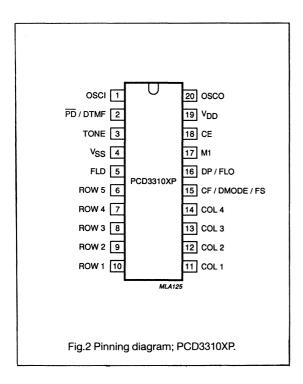

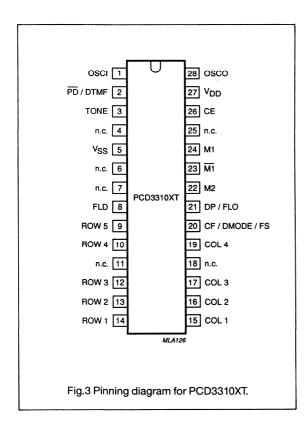

| PCD3310P      | pulse and DTMF dialler with redial; pulse dialling mark/space ratio 2:1; PABX                                                                                                                                                | 485  |

| PCD3310T      | register; notepad; flash; access pause by cursor method pulse and DTMF dialler with redial; pulse dialling mark/space ratio 2:1; PABX register; notepad; flash; access pause by cursor method                                | 485  |

| PCD3310AP     | variant of PCD3310 with markspace ratio 3:2                                                                                                                                                                                  | 485  |

| PCD3310AT     | variant of PCD3310 with markspace ratio 3:2                                                                                                                                                                                  | 485  |

| PCD3310CP     | variant of PCD3310; dialling mode indicator output                                                                                                                                                                           | 485  |

| PCD3310CT     | variant of PCD3310; dialling mode indicator output                                                                                                                                                                           | 485  |

| PCD3310EP     | PCD3310 with 20 Hz dialling frequency                                                                                                                                                                                        | 485  |

| PCD3310ET     | PCD3310 with 20 Hz dialling frequency                                                                                                                                                                                        | 485  |

| PCD3310FP     | PCD3310 with DTMF 60/90 ms tone burst                                                                                                                                                                                        | 485  |

| PCD3310FT     | PCD3310 with DTMF 60/90 ms tone burst                                                                                                                                                                                        | 485  |

| PCD3310GP     | PCD3310 with pulse/DTMF switching                                                                                                                                                                                            | 485  |

| PCD3310GT     | PCD3310 with pulse/DTMF switching                                                                                                                                                                                            | 485  |

| PCD3310HP     | PCD3310 with pulse/DTMF switching                                                                                                                                                                                            | 485  |

| PCD3311CP     | DTMF/modem/music tone generators with binary-coded parallel input or serial data input; I <sup>2</sup> C-bus                                                                                                                 | 509  |

| PCD3311CT     | DTMF/modern/music tone generators with binary-coded parallel input or serial data input; I <sup>2</sup> C-bus                                                                                                                | 509  |

## Numerical index

| type number                                                   | description                                                                                                                                                                                                                                           | page                            |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| PCD3312CP                                                     | DTMF/modem/music tone generators with binary-coded parallel input or serial data input; I <sup>2</sup> C-bus                                                                                                                                          | 509                             |

| PCD3312CT                                                     | DTMF/modem/music tone generators with binary-coded parallel input or serial data input; I <sup>2</sup> C-bus                                                                                                                                          | 509                             |

| PCD3315P                                                      | CMOS microcontroller for telephone sets; 160 x 8 RAM; 15K x 8 ROM; –25 to +70 °C                                                                                                                                                                      | 527                             |

| PCD3315T                                                      | CMOS microcontroller for telephone sets; 160 x 8 RAM; 15K x 8 ROM; –25 to +70 °C                                                                                                                                                                      | 527                             |